Hello,

I clock the PCM1863 on the SCKI pin with 27.000MHz

Using the formula from chapter 8.13.5 I calculate my PLL settings:

PLLCKIN is 27MHZ (video clock)

PLLCK selected to be 98.304MHz

PLLCK = (PLLCKIN*R*K) / P

values calculated:

P=2, R=1, K=7.2818

K splits up in J and D: J=7 D=2818

On page 34 it says "6.667MHz = PLLCLK _IN / P = 20MHz", which probably means "6.667MHz < PLLCLK _IN / P < 20MHz", so at 27MHz P must be at least 2, so I selected P=2.

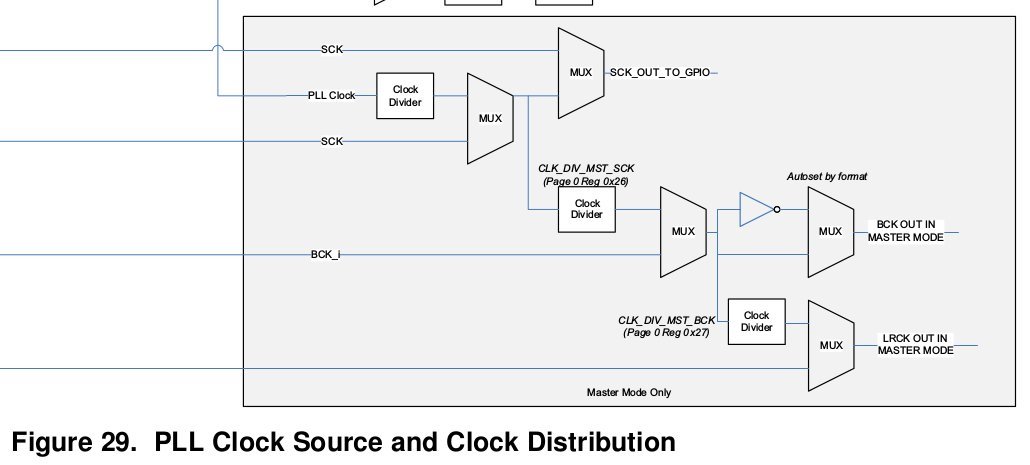

Page 35 mentions 'N' but that information does not help much. I guess N=2048 in the examples is just the dividers in I2C regs 0x25, 0x26, 0x27 which are 8*4*64

Writing registers on page 0:

0x0 0x0 (select page 0)

0x20 0x5E (set clock src to scki, disable auto clk detect, PLL clock as source for modules)

0x25 0x7 (PLL SCK Clock Divider value 1:8)

0x26 0x3 (Ratio of Master clock (SCK) to Bit Clock (BCK) 1:4)

0x27 0x3F (SCK to LRCK ratio in master mode 1:64)

0x28 0x1 (enable PLL)

0x29 0x1 (P=2)

0x2a 0x0 (R=1)

0x2b 0x7 (J=7)

0x2c 0xfc (D LSB)

0x2d 0x0a (D MSB)

(I assume the documentation is wrong and the limit for 2c is 0xffff, not 9999?)

With those settings and a SCKI input signal of 27MHZ I measure a LRCK of 105.4kHz and a BCK of 6.75 MHz

The ratio of LRCK to BCK is ok, but the frequency is wrong.

Assuming the unnamed clock divider in the grey box is controlled by 0x25, it is set to 1:8

I think P,J,D and R control the PLL settings (also Fig 29, not in the screen shot)

Trying to understand the output I get:

LRCK=105 kHz -> reg 0x27 is 1:64 -> BCK = 6.75MHz -> reg 0x26 is 1:4 -> 27MHz

How is the unnamed MUX (clock div / SCK) controlled?

Is this one maybe directly sourcing the 27 MHz via SCK?

Can someone please review my register settings?

Best regards,

Lo