Hello!

Even though there are posts related to this topic and read them, not able to figure out what is the problem is my setup.

What I have been doing is as follows

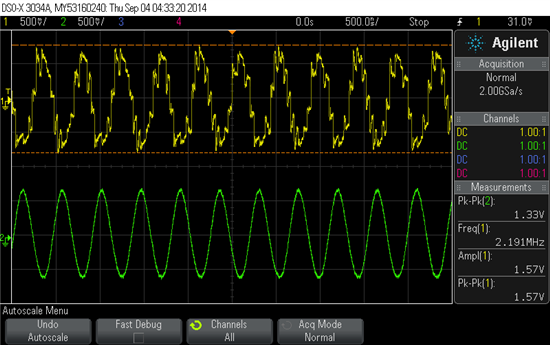

1. Giving a input signal of 2 MHz and a clock of 48MHZ to ADC.

2. The digital data coming out of ADC is being written if a FIFO (which I have defined in FPGA) with write clock of 96 MHz which is the output of MMCM block(1) in FPGA, and the input to this MMCM block(1) is coming from ADC itself (Same clock of 48 MHz that is provided to ADC as clock).

3. Reading the FIFO with a clock of 96 MHz which is the output of another MMCM block(2) in FPGA and input to this MMCM block(2) is coming from the DAC board.

4. The output of MMCM block(2) is also being used for DATA_CLK for DAC.

In short there are two MMCM block in my design and and I am feeding them from different clocks.One clock is coming through ADC (generated from High frequency function generator) and other is coming through DAC which is generated by CDCE62005.

And I am using FMC connectors to connect ADC and DAC to FPGA board.

Problem is: I am not getting any signal at the output of DAC, which is expected to be 2 MHz signal that I feed to ADC. I wanted to attach the DAC configuration file as well as VHDL code. but there is no link where i can do so.

Please help!

Regards

Pramod singh