Quite a while back, I was working on a project involving the DAC34H84, the thread seen here. With the high noise in the synthesis unresolved, I moved on to troubleshoot other parts of the system.

I am trying again to get this DAC to produce a clean signal, and am still turning up with an ugly, misshaped signal. This is largely based off of the example

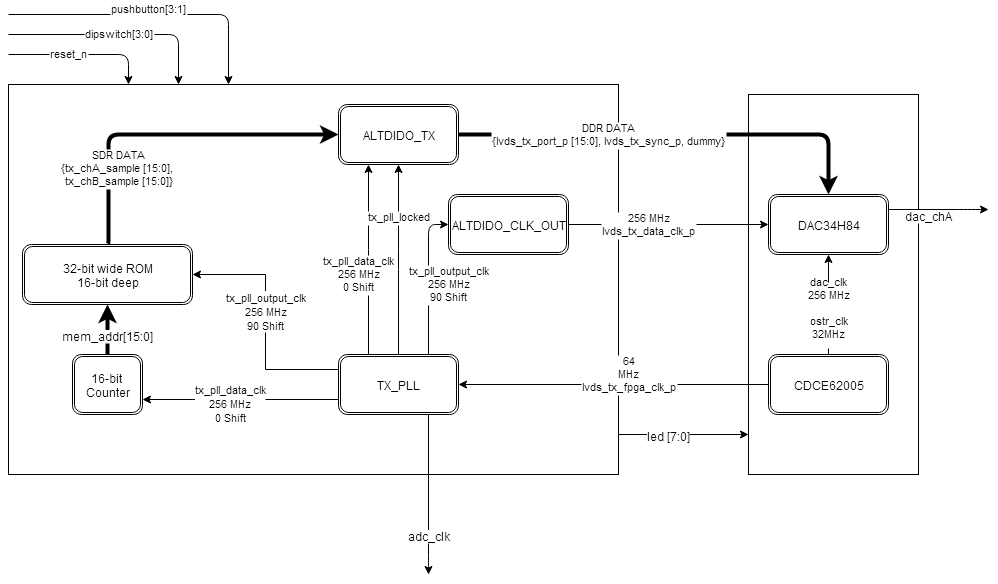

The function is as described below. The CDCE62005 generates a clock used to generate all other clocks on the TSW1400. A clock signal is send to a 16-bit counter, the output of which feeds to the address input of ROM. The ROM contains the signal to be created with the DAC, and is clocked 90 degrees off of the counter. The ROM is 32-bits wide, so each word contains both the channel A and channel B signals. This is fed to ALTDIDO_TX which is clocked -90 degrees out of phase of the memory. ALTDIDO_TX combines the two 16-bit SDR data streams into a single DDR 16-bit data stream..

TX_PLL is fed into ALTDIDO_CLK_OUT which create the clock corresponding to the DAC data.

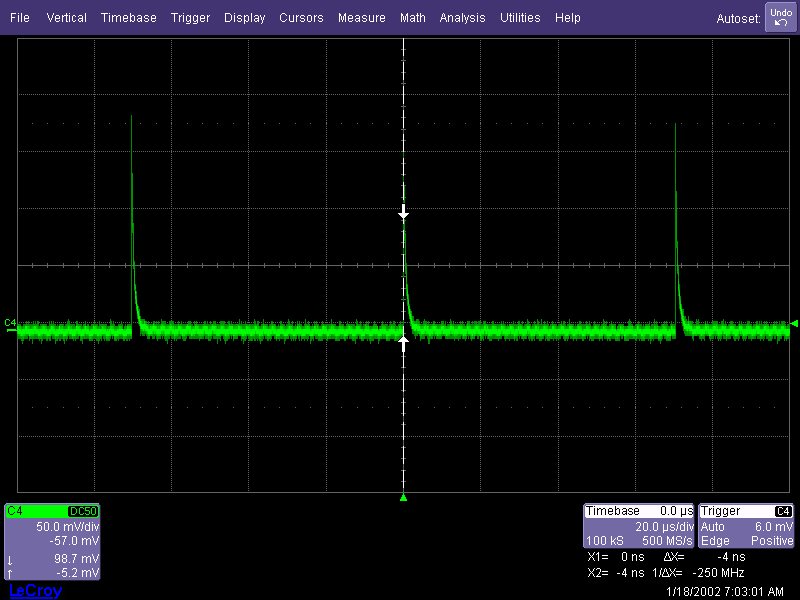

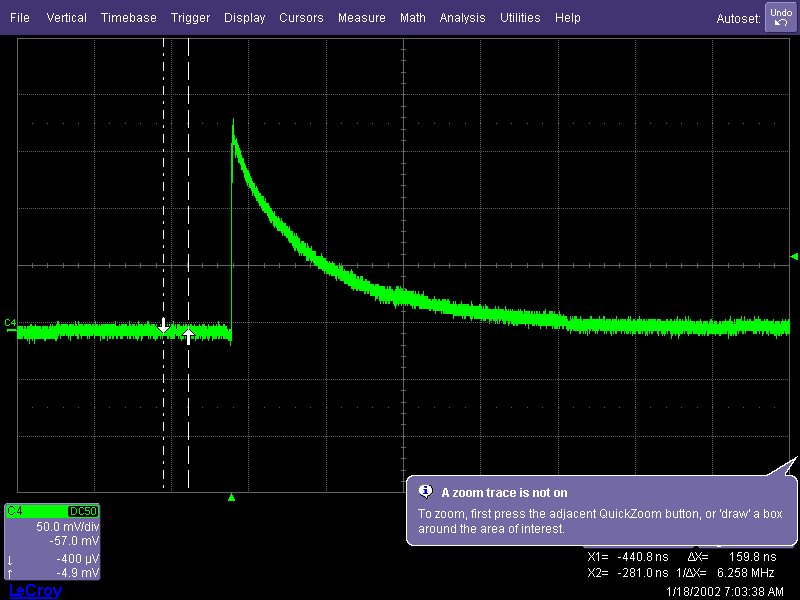

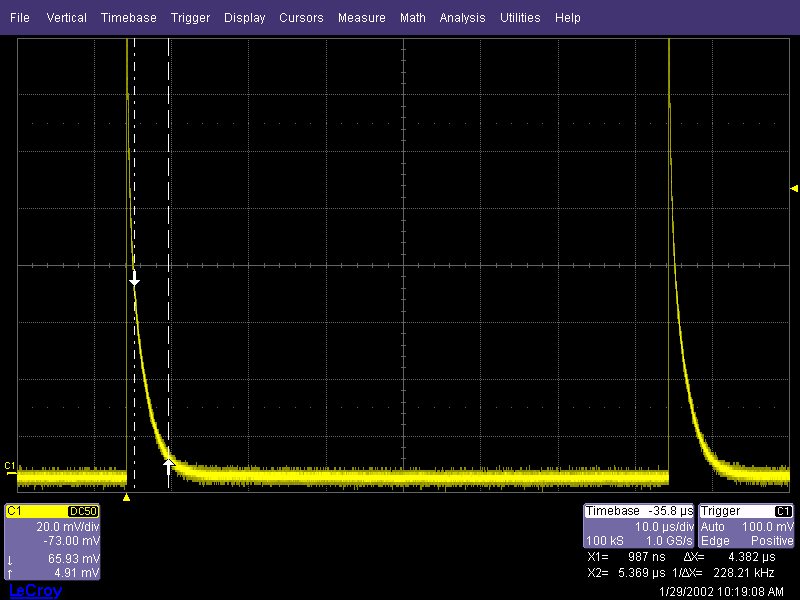

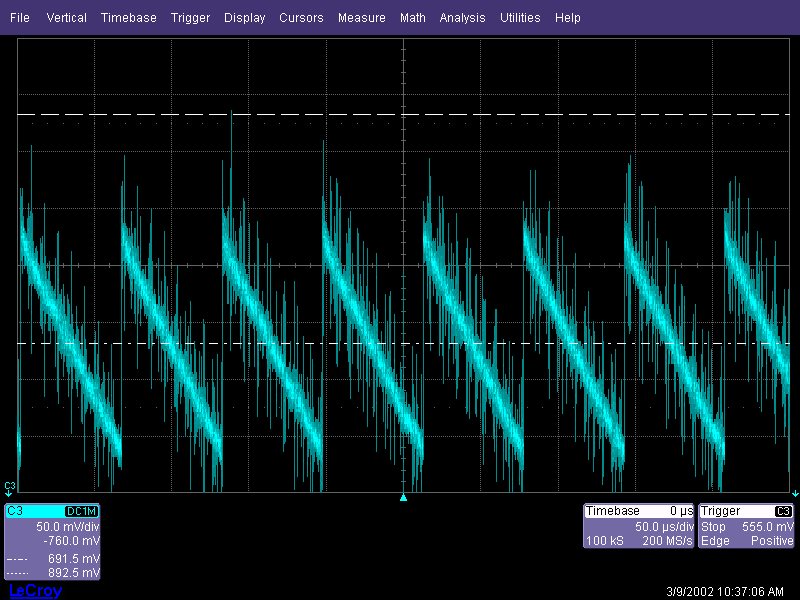

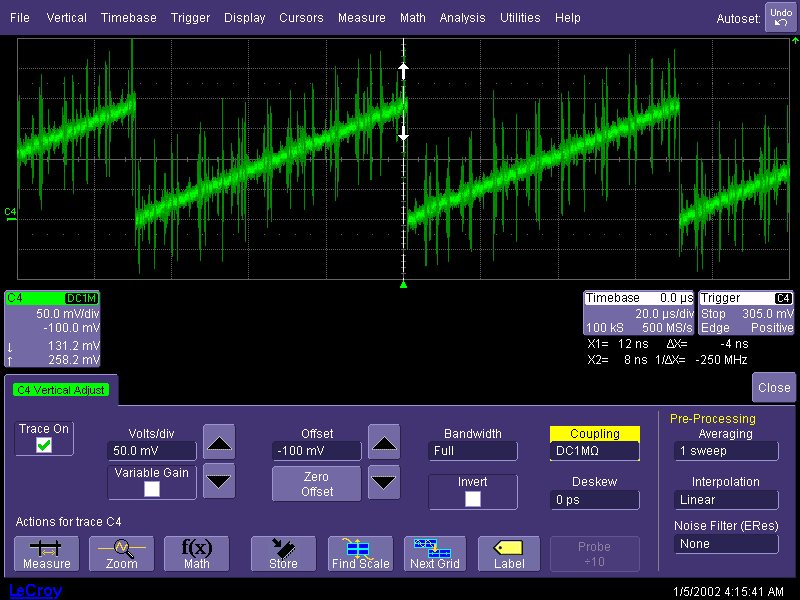

With this setup, I am getting a lot of systematic 'noise' from the DAC, similar to my problems previously, and there is huge distortion on the signal. Here is an example of a ramp signal sent to the DAC: