Other Parts Discussed in Thread: AM1808, , , TMS570LC4357, LAUNCHXL2-570LC43

Tool/software: TI C/C++ Compiler

Hi,

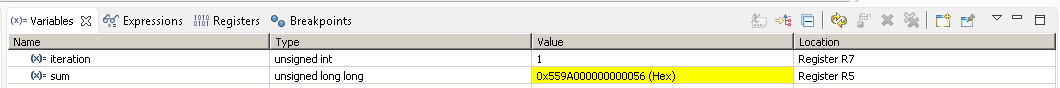

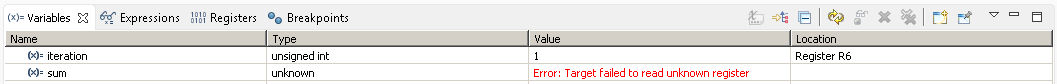

I am using CCS6.1 with compiler 5.22. I found the result of multiplication of two 32-bits data is not correct. I defined the result as 64 bits data. the correct result should be 0x0000 0056 0038 7512. I saw one register R0 has the number 0x0000 0056, another register R1 has the number 0x00387512, which is correct. however, the result I get is 0x0038 7512 0000 0056, which seems the two registers's data are put in the wrong order.

Is it a bug or I didn't configure the CCS correctly?

Thanks,

Julie