Hi,

My customer is using the C5517.

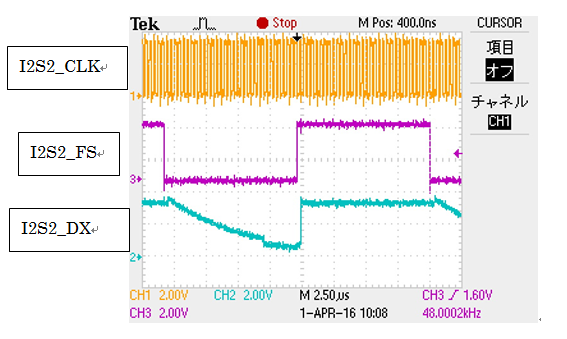

Their board has encountered a problem that I2S2 of L channel is not output correctly.

I will present in more detail below.

[Configuration and, I2S2 setting of the board]

- C5517 reference clock : 12.288Mhz

- I2S2 configuration

- system clock : 196.608Mhz

- Master mode : bit clock and frame sync generate by C5517

- bit clock frequency : 3.072Mhz

- frame rate : 48khz

- Frame polarity : R channel is Low, L channel is High

- Data delay : 1bit

- Word length : 32bit

- Data format : I2S format

Please see attached file(main.c) and the observed waveform is shown below.

/*----------------------------------------------*/

/* I2S2 TX Interrupt (ISR) */

interrupt void i2s_tx_isr(void)

{

volatile unsigned short dummy;

dummy =(* (volatile unsigned int *)(0x2A10) );

(* (ioport unsigned short *)(0x2A09) ) = (unsigned short)(0xf0f0); /* I2STXLT2 (upper) */

(* (ioport unsigned short *)(0x2A08) ) = 0xf0f0; /* I2STXLT1 (lower) */

(* (ioport unsigned short *)(0x2A0D) ) = (unsigned short)(0xffff); /* I2STXRT2 (upper)*/

(* (ioport unsigned short *)(0x2A0C) ) = 0xffff; /* I2STXRT1 (lower) */

}

volatile signed short debug_sound_buf[2][256];

volatile unsigned short debug_sound_buf_index;

/*----------------------------------------------*/

/* I2S2 RX Interrupt (ISR) */

interrupt void i2s_rx_isr(void)

{

volatile unsigned short dummy;

dummy = (* (ioport volatile unsigned int *)(0x2A10) );

debug_sound_buf[0][debug_sound_buf_index] = (* (ioport volatile unsigned int *)(0x2A29) );

debug_sound_buf[1][debug_sound_buf_index] = (* (ioport volatile unsigned int *)(0x2A2D) );

debug_sound_buf_index ++ ;

}

/*----------------------------------------------*/

/* Main */

void main(void)

{

unsigned short tmp;

_disable_interrupts();

/* Interrupt Initialize */

(* (volatile unsigned short *)0x0001 ) = 0xFFFF; /* IFR0 */

(* (volatile unsigned short *)0x0046 ) = 0xFFFF; /* IFR1 */

(* (volatile unsigned short *)0x0000 ) = 0x0000; /* IER0 */

(* (volatile unsigned short *)0x0045 ) = 0x0000; /* IER1 */

// if((CPU.IVPD != BOOT_IVP) || (CPU.IVPH != BOOT_IVP)) {

// r = 0;

// }

(* (volatile unsigned short *)0x0049 ) = 0x0001; /* IVPD Interrupt Address -> 0x000100 */

(* (volatile unsigned short *)0x004A ) = 0x0001; /* IVPH Interrupt Address -> 0x000100 */

/* PLL off, Bypass Mode */

(* (ioport volatile unsigned short *)0x1C1F ) = 0x0000; /* CCR2 Register */

/* Wait Bypass Mode (4Cycles) */

asm( " repeat(#4) "); /* Wait 4Cycles */

asm( " NOP" );

/* PLL reset �z�[���h */

(* (ioport volatile unsigned short *)0x1C22 ) = 0x4000; /* PCR Register */

/* Set PLL Parameter */

(* (ioport volatile unsigned short *)0x1C20 ) = 16128; /* PMR Register */

(* (ioport volatile unsigned short *)0x1C21 ) = 0x0001; /* PICR Register */

(* (ioport volatile unsigned short *)0x1C23 ) = 0x0000; /* PODCR Register */

/* PLL reset release */

(* (ioport volatile unsigned short *)0x1C22 ) = 0x0000;

/* wait 4ms for PLL stabilization */

/* wait 4ms (49152cycle at 12.288MHz clock frequency) */

asm( " repeat(#49152) "); /* Wait Cycles 81ns * 49152=4ms */

asm( " NOP" );

/* PLL on */

(* (ioport volatile unsigned short *)0x1C1F ) = 0x0001;

/* ST3_55 CLKOFF bit */

tmp = (* (volatile unsigned short *)0x0004 );

tmp |= 4; /* write 1 to clkoff bit */

(* (volatile unsigned short *)0x0004 ) = tmp;

// (* (ioport volatile unsigned short *)0x1C24 ) = 0x8001; /* CLKOUTCR */

(* (ioport volatile unsigned short *)0x1C24 ) = 0x8000; /* CLKOUTCR */

/* EBSR setting */

(* (ioport volatile unsigned short *)0x1C00 ) = 0x153c;

/* Clock Gating */

(* (ioport volatile unsigned short *)0x1C02 ) = 0x34F9;

(* (ioport volatile unsigned short *)0x1C03 ) = 0x003d;

(* (ioport volatile unsigned short *)0x1C04 ) = 0x0008;

(* (ioport volatile unsigned short *)0x1C05 ) = 0x00ff;

asm( " repeat(#8)"); /* Wait Cycles 81ns * 49152=4ms */

asm( " NOP" );

/* I2s2 Setting */

(* (ioport volatile unsigned short *)0x2A00 ) = 0x0022; /* I2S2SCTRL */

(* (ioport volatile unsigned short *)0x2A04 ) = 0x001d; /* I2S2SRATE */

/* bit clock = 196.608MHz / 64 = 3.072MHz, frame = 3.072MHz / 64 = 48kHz */

(* (ioport volatile unsigned short *)0x2A14 ) = 0x0028; /* I2S2INTMASK */

tmp = (* (ioport volatile unsigned short *)0x2A00 ); /* I2S2SCTRL */

tmp |= 0x8000; /* enable bit ON */

(* (ioport volatile unsigned short *)0x2A00 ) = tmp;

tmp = (* (volatile unsigned short *)0x0000 ); /* IER0 */

tmp |= 0xC000; /* RCV2 bit ON , XMT2 bit ON */

(* (volatile unsigned short *)0x0000 ) = tmp;

debug_sound_buf_index = 0; /* initialize buffer index */

_enable_interrupts();

while(1);

}

[About the phenomenon]

- Lch is not output correctly sometimes occur.

- the frequency of occurrence of the problem is changed by the PCGCR1/2 register setting.

- It seems that the frequency is reduced when the clock supply to all peripherals

- in slave mode is no problem.

- I2S0 and I2S3 is no problem in master mode with same I2S config.

Do anyone happen to have any knowledge about this phenomenon?

Please point out if you know the cause.

Best regards,

H.U