Hi,

I have question about IDLE3 procedure for C5517.

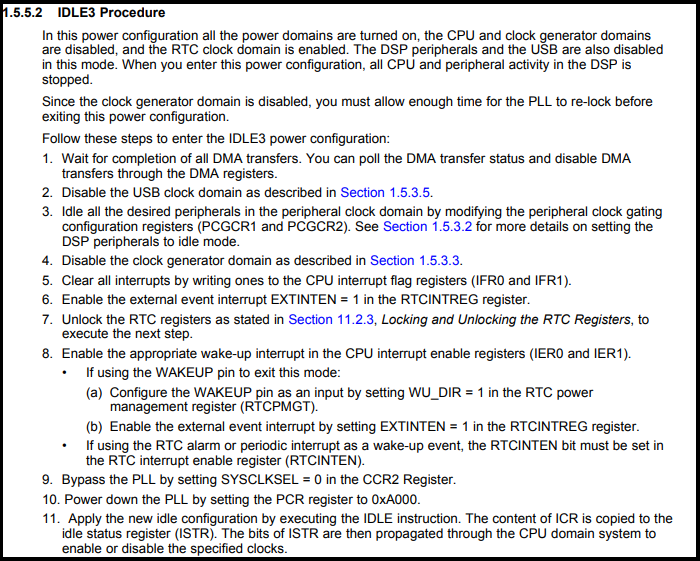

I am planning to execute processing according to the IDLE 3 procedure described in the following document(SPRUH16B).

However, it seems that disabling the CPU domain is missing compared with CSL's sample software(\\c55_csl_3.08\ccs_v6.x_examples\power\CSL_PowerManagement_IDLE3_Example\csl_power_management_idle3_example.c).

For example, disabling the system clock by PCGCR1.SYSCLKDIS and setting the CPU domain by idle configuration register (ICR) exist in the CSL sample.

Which procedure is correct?

If the system clock is disabled by SYSCLKDIS=1, there is a phenomenon that returning to IDLE3 sometimes does not return normally when repeating Enter / Return to IDLE3. So, is it impossible to disable the system clock?

Best regards,

H.U