Hi,

I'm working with the internal loopback example found in the folder:

C:\Program Files\Texas Instruments\pdk_C6678_1_0_0_11\packages\ti\drv\exampleProjects\SRIO_LoopbackTestProject

1.- Could you tell me, please, which is the SRIO Bit Rate configured?

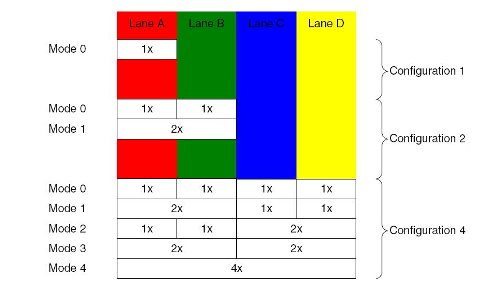

2.- Could you tell me, please, which is the lines configuration?

Thanks in advance.

shmulik