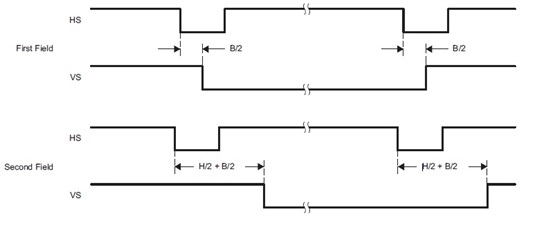

Because TVP5147M1 output Y[2:9] is connected to VIN1[8:16] on the 8148EVM, 10bit embeded sync mode cannot be used for video capture. I am now using 20 bit discrete sync mode of TVP5147M1. But I meet problems below:

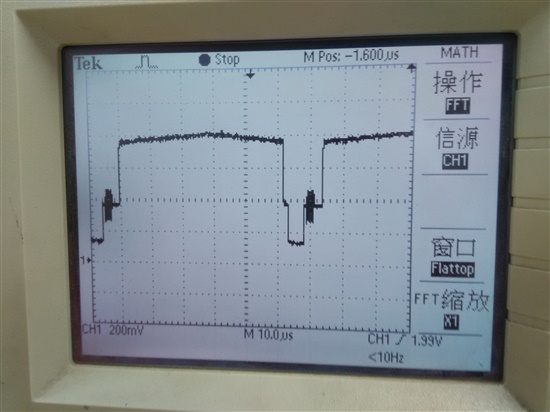

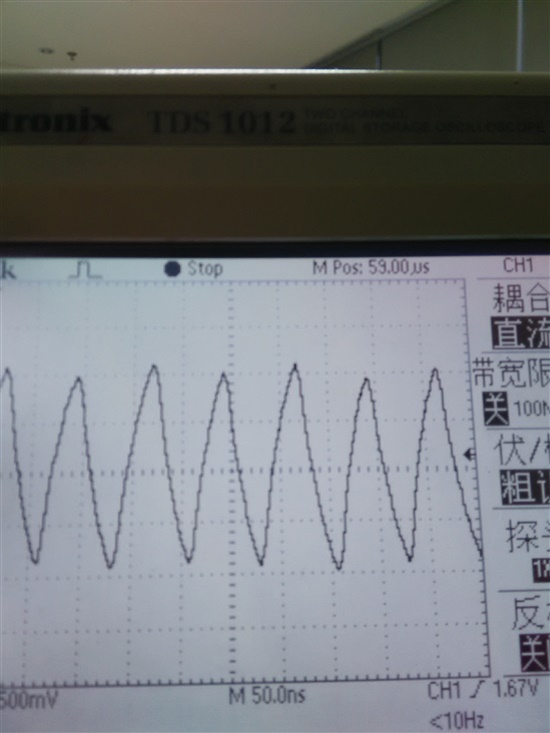

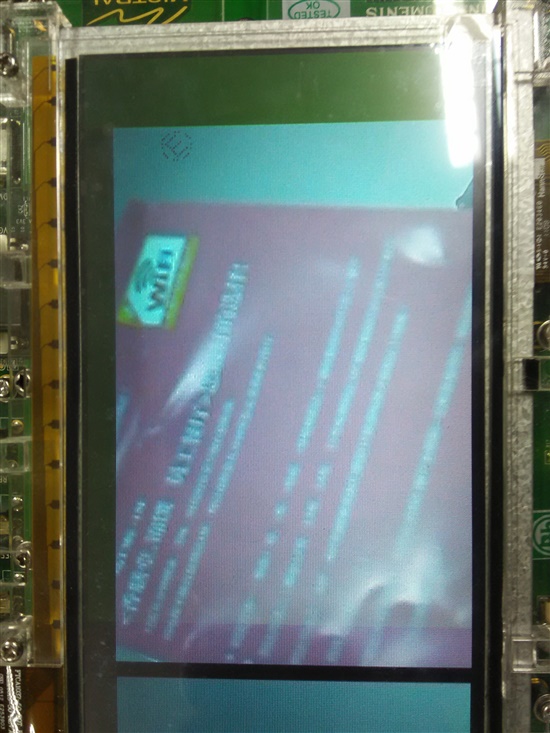

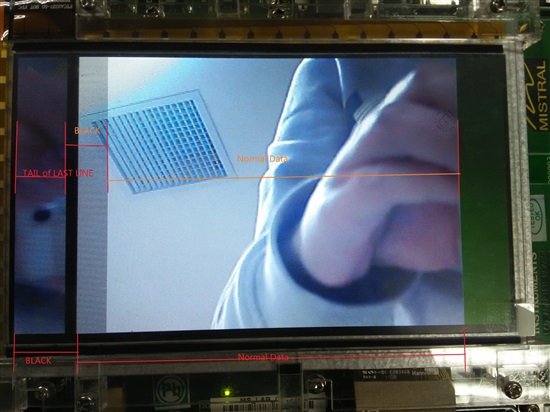

1) 5147M1 can't always get sync locked with PAL camera signal. Sometime it can get sync locked and othertime it can't.

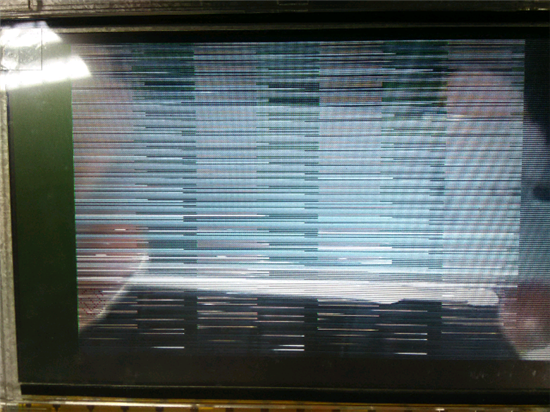

2) When 5147M1 get sync locked with camera, weak singal mode is detected, video data is not correct. So I doubt that 5147 is not really sync with camera.

Below are registers values of TVP5147M1

tvp514x 3-005c: Standard set to: PAL

tvp514x 3-005c: Reg(0x00): 0x05

tvp514x 3-005c: Reg(0x01): 0x0F

tvp514x 3-005c: Reg(0x02): 0x02

tvp514x 3-005c: Reg(0x03): 0x30

tvp514x 3-005c: Reg(0x04): 0x03

tvp514x 3-005c: Reg(0x05): 0x10

tvp514x 3-005c: Reg(0x06): 0x00

tvp514x 3-005c: Reg(0x07): 0x00

tvp514x 3-005c: Reg(0x08): 0x00

tvp514x 3-005c: Reg(0x09): 0x80

tvp514x 3-005c: Reg(0x0A): 0x80

tvp514x 3-005c: Reg(0x0B): 0x80

tvp514x 3-005c: Reg(0x0C): 0x00

tvp514x 3-005c: Reg(0x0D): 0x00

tvp514x 3-005c: Reg(0x0E): 0x04

tvp514x 3-005c: Reg(0x10): 0x80

tvp514x 3-005c: Reg(0x11): 0x80

tvp514x 3-005c: Reg(0x12): 0x80

tvp514x 3-005c: Reg(0x14): 0x80

tvp514x 3-005c: Reg(0x16): 0x5F

tvp514x 3-005c: Reg(0x17): 0x00

tvp514x 3-005c: Reg(0x18): 0x2F

tvp514x 3-005c: Reg(0x19): 0x03

tvp514x 3-005c: Reg(0x1A): 0x07

tvp514x 3-005c: Reg(0x1B): 0x00

tvp514x 3-005c: Reg(0x1C): 0x47

tvp514x 3-005c: Reg(0x1D): 0x00

tvp514x 3-005c: Reg(0x1E): 0x01

tvp514x 3-005c: Reg(0x1F): 0x00

tvp514x 3-005c: Reg(0x20): 0x04

tvp514x 3-005c: Reg(0x21): 0x00

tvp514x 3-005c: Reg(0x22): 0x6F

tvp514x 3-005c: Reg(0x23): 0x02

tvp514x 3-005c: Reg(0x24): 0x18

tvp514x 3-005c: Reg(0x25): 0x00

tvp514x 3-005c: Reg(0x32): 0x00

tvp514x 3-005c: Reg(0x33): 0x01

tvp514x 3-005c: Reg(0x34): 0x13

tvp514x 3-005c: Reg(0x35): 0xEE

tvp514x 3-005c: Reg(0x36): 0xAF

tvp514x 3-005c: Reg(0x37): 0xFF

tvp514x 3-005c: Reg(0x38): 0xFF

tvp514x 3-005c: Reg(0x39): 0x01

tvp514x 3-005c: Reg(0x3A): 0x6E

tvp514x 3-005c: Reg(0x3B): 0xD8

tvp514x 3-005c: Reg(0x3C): 0x00

tvp514x 3-005c: Reg(0x3D): 0x00

tvp514x 3-005c: Reg(0x3F): 0x02

tvp514x 3-005c: MBUS_FMT: Width - 720, Height - 576.

.