Hello

we are investigating on enabling cache on DM8168 DSP. We are running the "universal_copy" example in codec engine togheter with capture_encode OMX example. We get the buffer from capture component, pass the pointer to DSP and encode the result (a simple copy). We add these lines to the "all_syslink.cfg" (in ti-ezsdk_dm816x-evm_5_05_02_00/component-sources/codec_engine_3_22_01_06/examples/ti/sdo/ce/examples/servers/all_codecs).

if (myName == "DSP") {

var Cache = xdc.useModule('ti.sysbios.family.c64p.Cache');

var obj = new Cache.Size;

obj.l1pSize = Cache.L1Size_32K;

obj.l1dSize = Cache.L1Size_32K;

obj.l2Size = Cache.L2Size_128K;

Cache.initSize = obj;

Cache.MAR128_159 = 0xFFFFFFFF;

Cache.MAR160_191 = 0xFFFFFFFF;

Cache.MAR192_223 = 0xFFFFFFFF;

Cache.MAR224_255 = 0xFFFFFFFF;

}

We want to enable caching of the buffers allocated in SharedRegion2 on DSP. Enabling th caching we don't see any improvements, even if we use the universal copy alg in "release" mode using

xdc.loadPackage('ti.sdo.ce.examples.codecs.' + 'universal_copy.UNIVERSAL_COPY').profile = 'release';

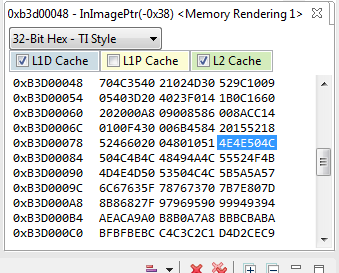

What do we need to enable Cache on DSP for Shared Region 2 buffers? We found also that using CCS6 and Memory Browser, the buffers are not painted with the colors of L2 Cache