Hi TI,

Starting design of some new boards and re-spinning of existing ones I have to repeat some questions that still remain unanswered (see OMAP-L138 I2C - spike on SCL).

Problem summary:

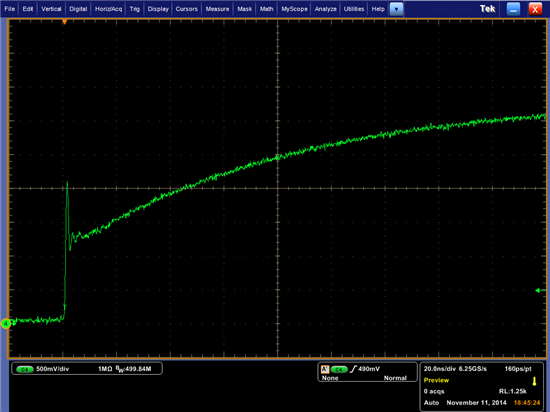

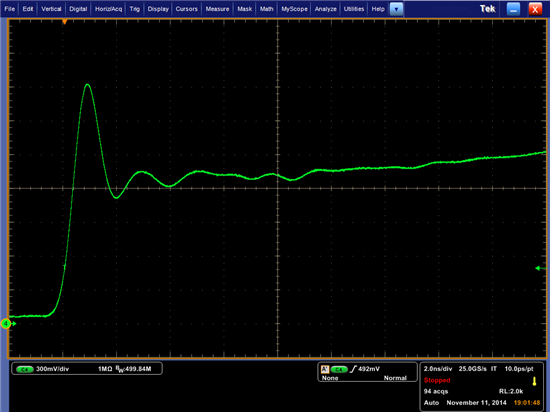

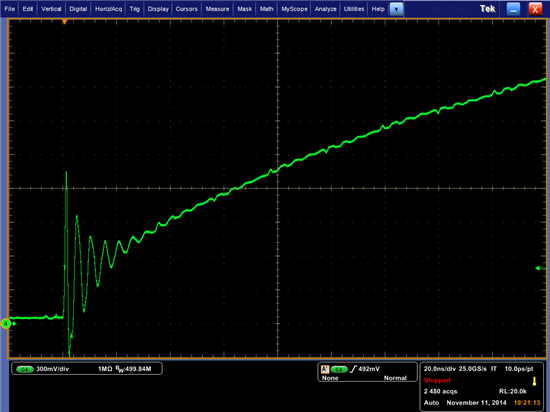

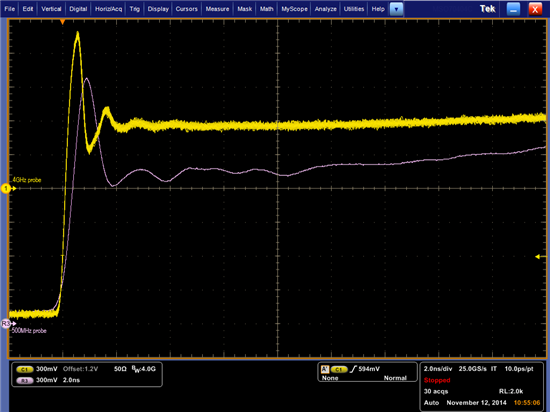

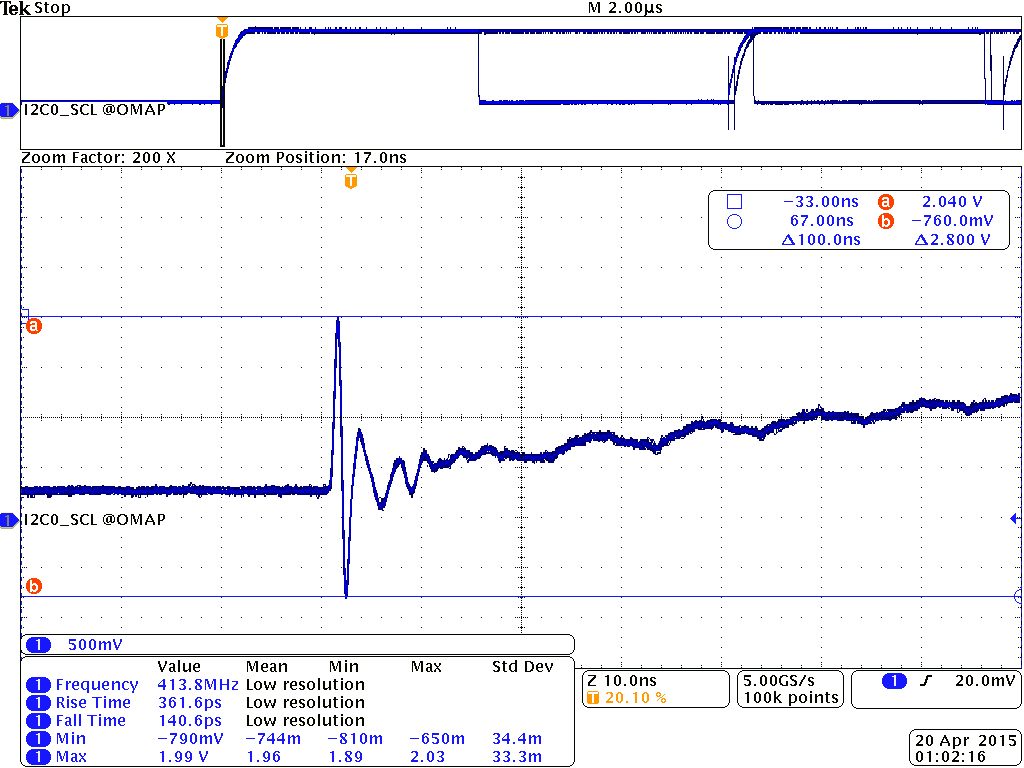

There is a short spike on the SCL line of OMAP-L138 I2C0 working in master mode at the beginning of low-to-high transition. I have observed this spike at some revisions of my custom boards using L138A (silicon revision 1.1).

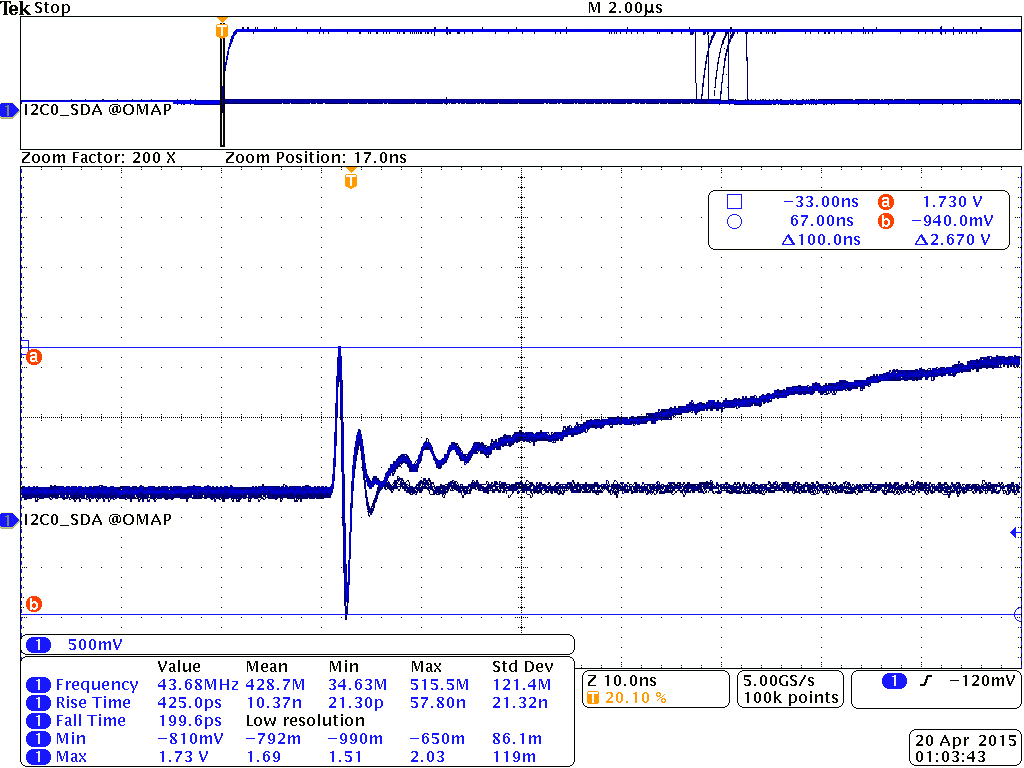

Similar issue has been recognized and corrected an year ago at least on AM335x - see Advisory 1.0.26 "I2C: SDA and SCL Open-Drain Output Buffer Issue" in AM335x Silicon Errata (background story: I2C1_SCL strange signal (AM3359), AM3352 unreliable I2C operation).

In addition to AM335x and OMAP-L138, at least OMAP3530 seems affected also (and again not corrected yet...) - see PCA9517 - Extra Spike on I2C

I suppose this issue must be reflected in errata anyway (even if TI have already corrected it or doesn't plan to fix it).

Question №1: what silicon revisions of OMAP-L138 are affected?

Question №2: what processor families (at least of AM1808, C6748, C6745, OMAP-L137) are potentially affected also?

BR,

Denis