Other Parts Discussed in Thread: DS90UB960-Q1,

Hello friends,

I've have the following system working..

4k60 test pattern generator split into even & odd lines and converted to two CSI-2 streams. Streams are input to DS90UB953 serializers and sent (over coax) to attached DS90UB954 deserializer. 954 can output correct rebuilt test pattern frames as CSI-2 from the received interleaved data if I run the system at 36 fps. If I run it at speed (60fps) the output of the 954 lines are corrupted and the actual output line count is short. (see images below for better understanding, please) I need best thoughts on what may be happening here. I don't think this is just a simple signal integrity issue. I looks more like a fifo overflow issue by how the lines are broken off at the same point in each data set. This could be due to the 954 not successfully seeing line ends or frame ends, but I don't really know. Looking for ideas.

Input to channel #1 953:

The input to the 1st 953. (0xff, oxff, 0xaa, 0xaa, 0xaa, 0xaa, 0x00, 0x00) (each of the preceding numbers is actually 600 bytes or 480 10bit words for a total line length of 3840 pixels)

Input to channel #2

The input to the 2nd 953. (0xff, 0xaa, 0xff, 0xaa, 0xaa, 0x00, 0xaa, 0x00) (each of the preceding numbers is actually 600 bytes or 480 10bit words for a total line length of 3840 pixels)

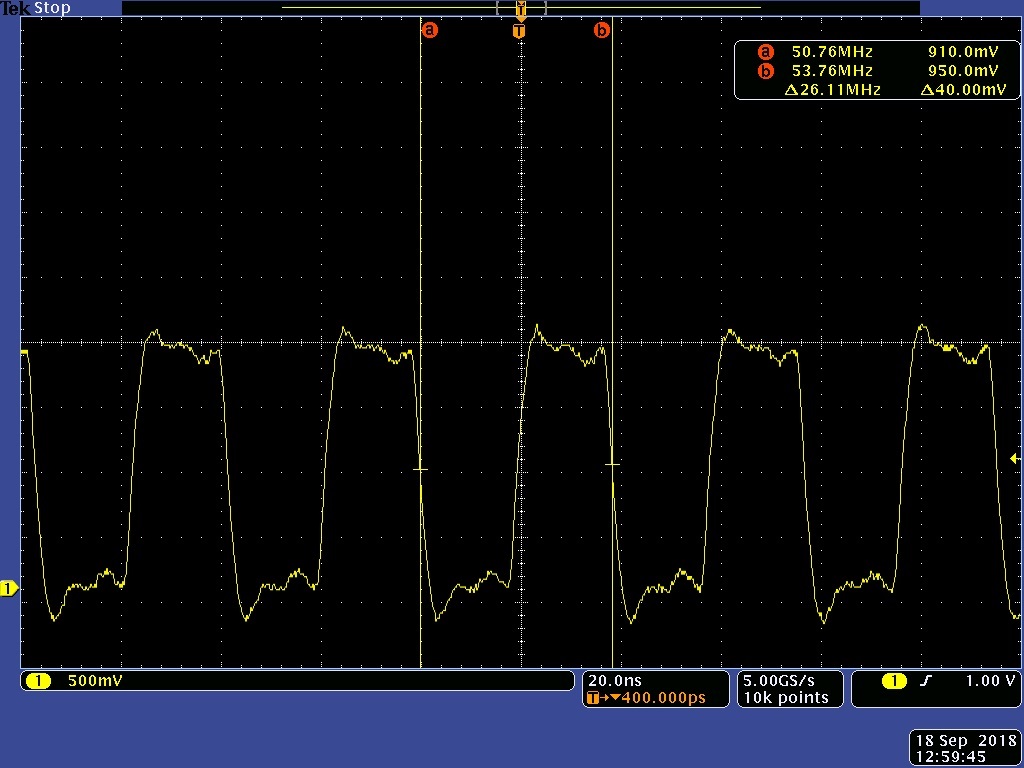

953 input frame rate:

You can see that the input frame rate to the 953's is roughly 16.92ms or 59.1Hz.

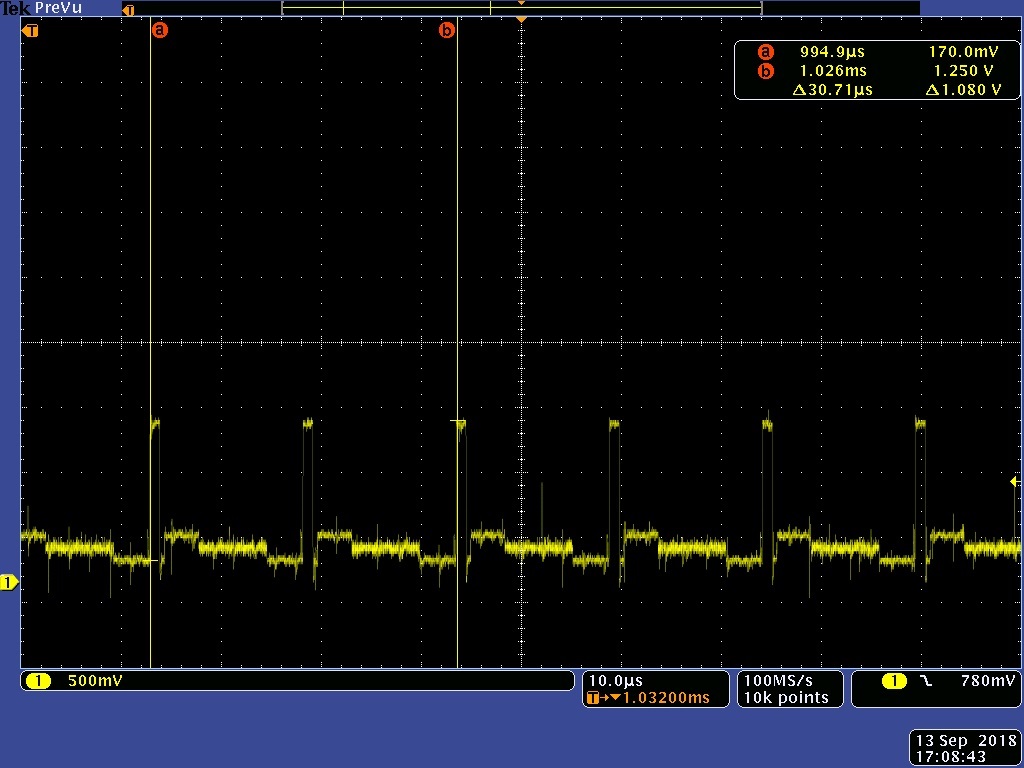

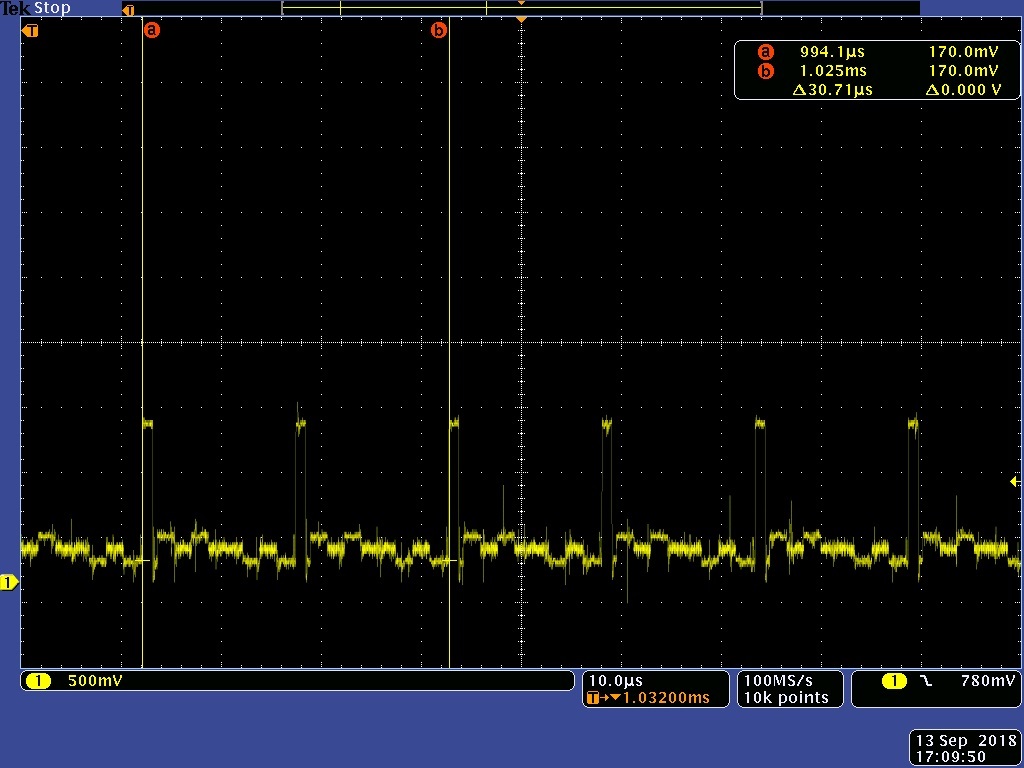

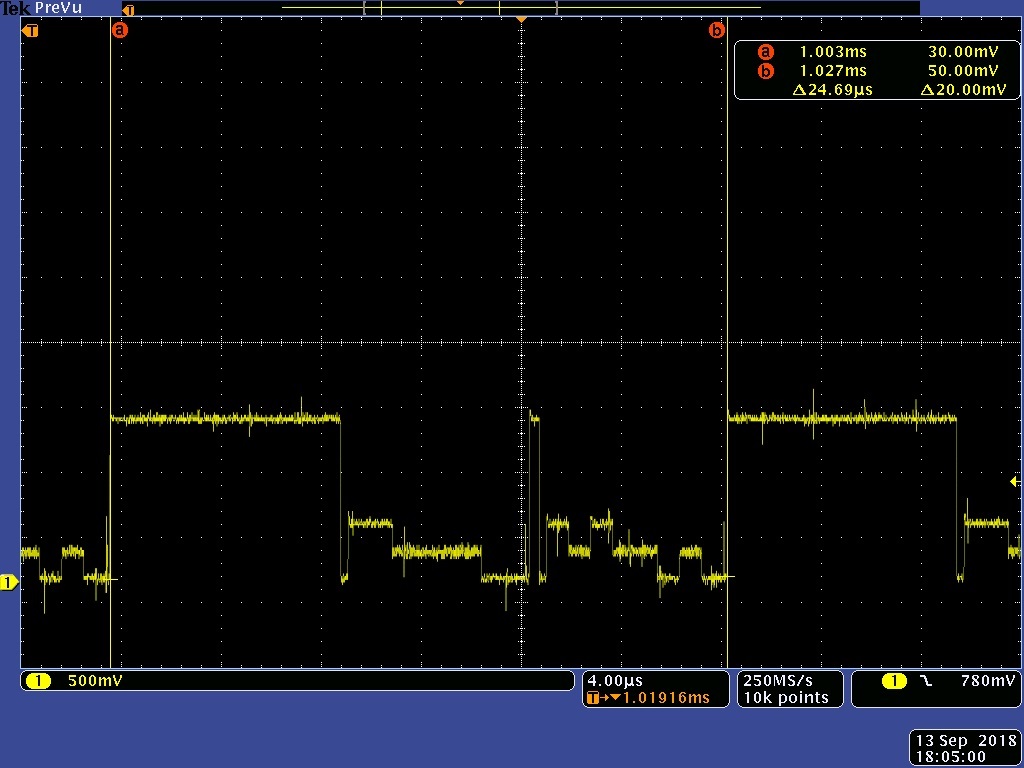

954 CSI-2 output:

These are the recombined interleaved lines from the 954 CSI-2 output. You can see the the beginning of each line is correct but the back half of the line data is not present... the total time for each line looks correct (if you measure between two counts of the LP11 portions of the stream) as two input lines to the 953 took 37.91usecs and two lines out of the 954 takes about half that amount. This is to be expected since we had two CSI-2 streams at the 953's and only one at the 954 --> should be twice as fast.

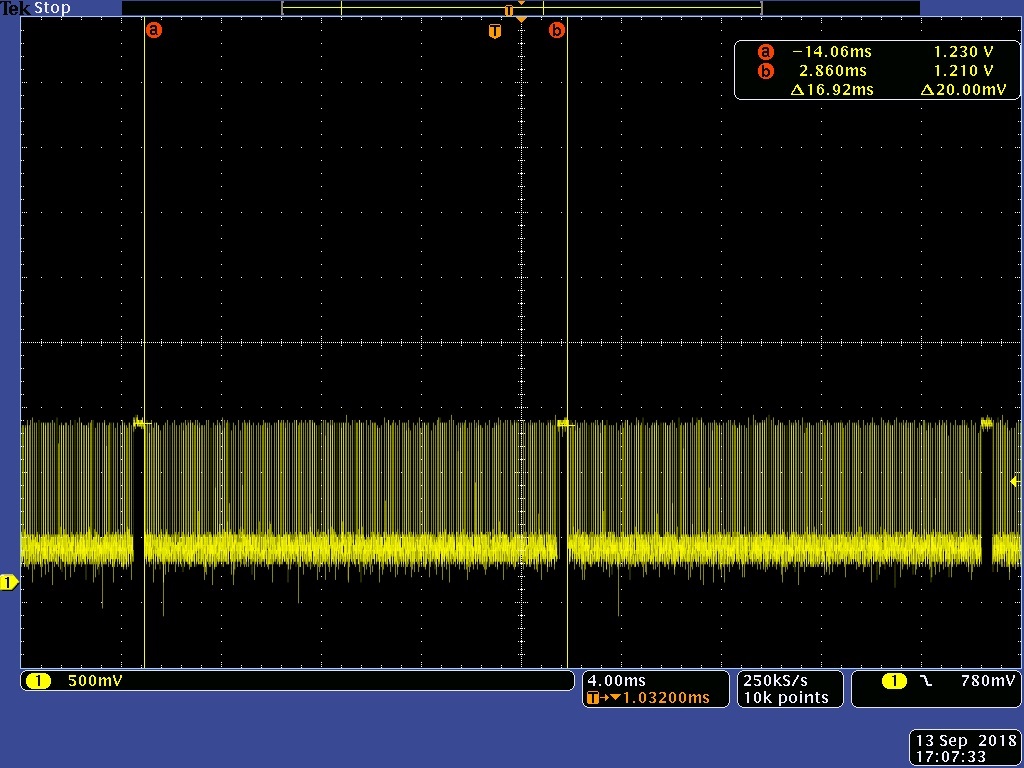

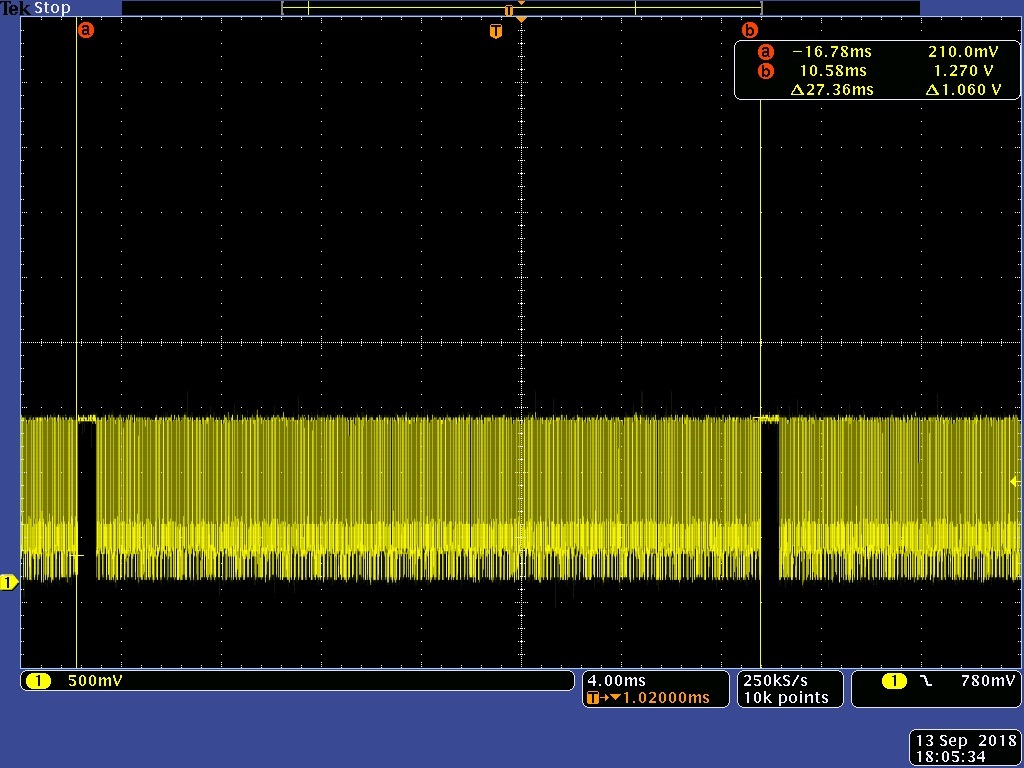

954 CSI-2 output per frame:

These are the lines in any given single frame. From the previous image it can be seen that the actual line lengths are correct but from this image you can see that the total line count per frame is only taking 2.04msec but should be taking 16.92msec. Lines (albeit incorrect data) are moving at the correct rate but the count is short.

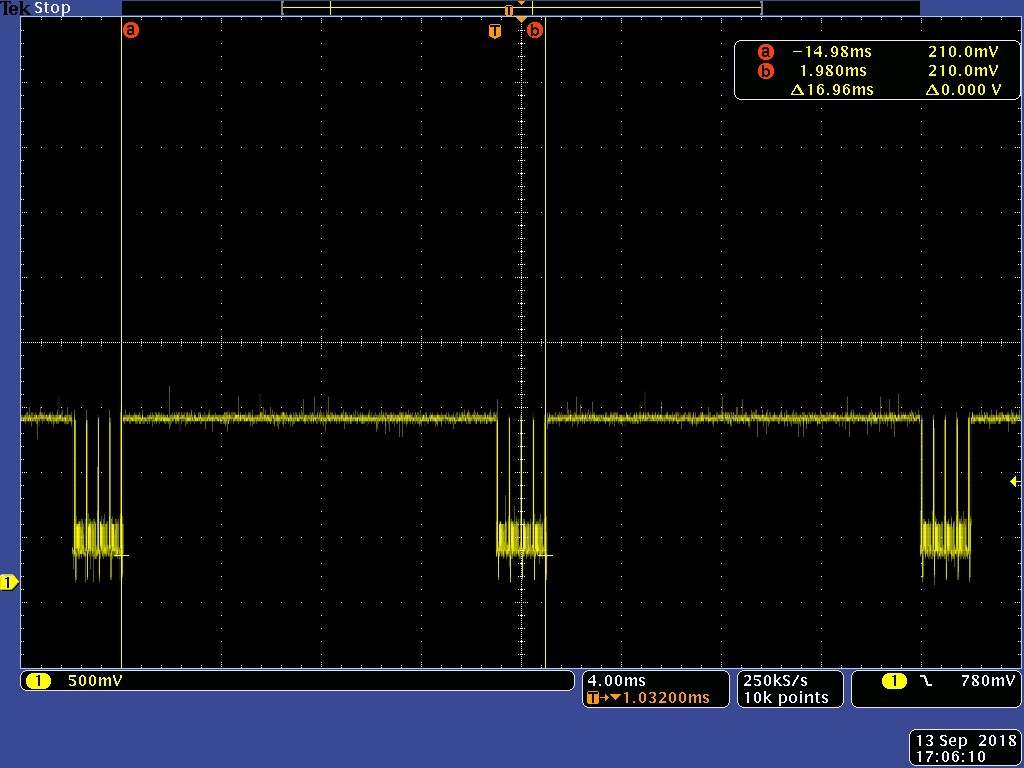

954 frame rate:

Note that the actual time between frame starts is correct (roughly 16.96msec) but the data (line count) has been truncated. Remember that 16.96ms or 58.96Hz which is about the same as what we measured at the input to the 953's. So the frame rate is correct.

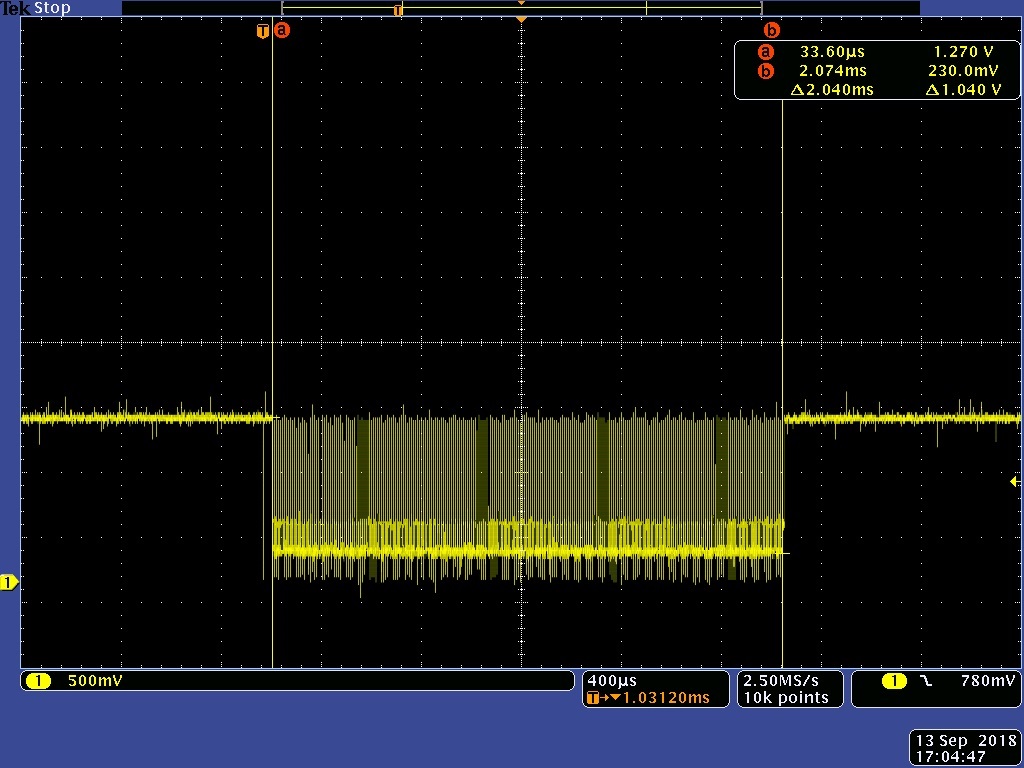

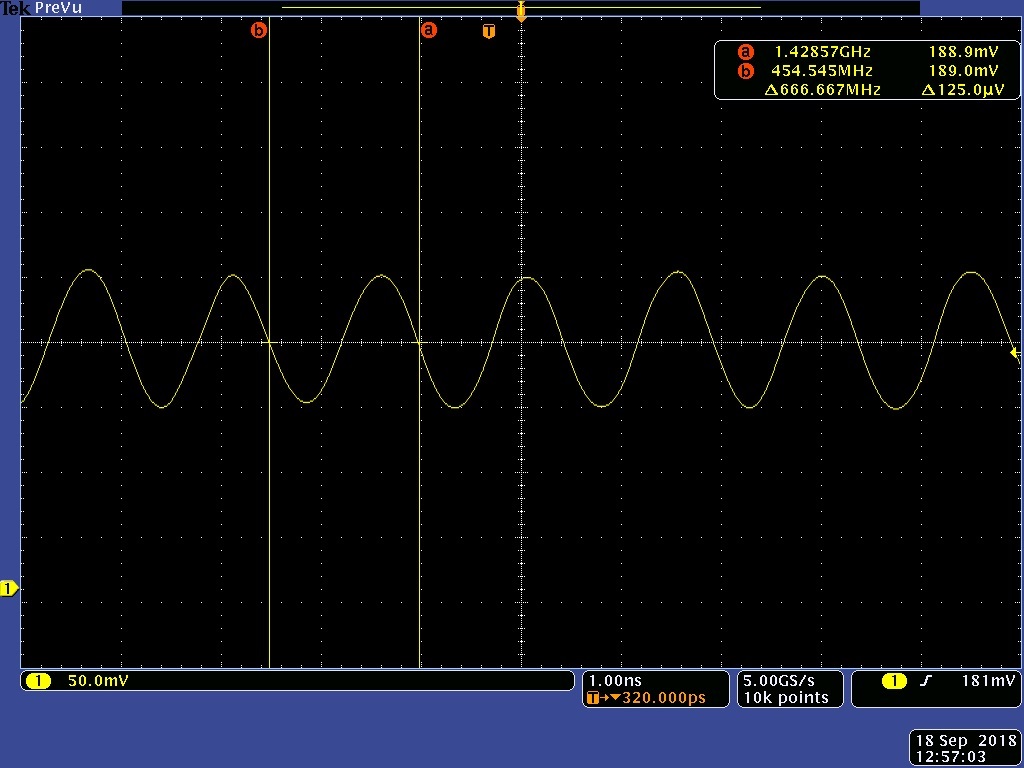

954 CSI-2 output when running 37fps:

If I run the system from a slower refclk from channel #1 953 where I get only 36fps I get a waveform that is correct out of the 954 as shown below. If you go back to the very top two images you will see that the recombined interleaved data below is correct.

line #1 = (0xff, oxff, 0xaa, 0xaa, 0xaa, 0xaa, 0x00, 0x00) (each of the preceding numbers is actually 600 bytes or 480 10bit words for a total line length of 3840 pixels)

line #2 = (0xff, 0xaa, 0xff, 0xaa, 0xaa, 0x00, 0xaa, 0x00) (each of the preceding numbers is actually 600 bytes or 480 10bit words for a total line length of 3840 pixels)

954 CSI-2 output frame rate when running 36fps:

thanks,

david