Hello Team,

I have a customer who is having issues with the DS90CF384 and wants to verify if the internal fail safe circuitry of this device is causing an overall failure of the product/ system. The description is below:

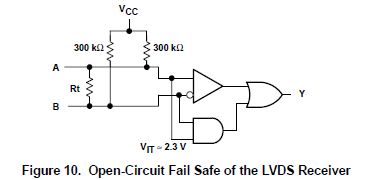

Can you clarify the type of fail-safe circuit the DS90CF384 has? In the application note it mentions a few types. TI seems to have two fail-safe circuit configurations – the type shown below and also a Window Comparator.

Based on the information I put together – the DS90CF384 is compliant with TIA/EIA-644 LVDS Standards. This means it has fail-safe functions implemented with internal pull-ups on each signal of the differential pair as shown below. My customer is trying to understand if it is possible for the inputs of this LVDS receiver to over-load the outputs of the device driving it? My understanding is once a valid signal is present on the differential input to the LVDS receiver it would not be possible to “lock-up” the device that is driving these valid signals. Can you confirm this?

Below are parts of schematics ( will be emailed separately ) showing the MIPI-DSI Bridge to LVDS (SN65DS183ZQER) part my customer is using. Also shown to the far right is the LVDS receiver on the Sharp LCD PCB. What I would really like to understand is if there is any way the LVDS receiver on the Sharp display PCB can cause the LVDS outputs (of the MIPI Bridge) to all of a sudden stop working properly? Once power is cycled everything works properly again. At the time of the MIPI bridge LVDS output failure there is nothing being done to the system. It is just sitting on a test station powered on and displaying the home screen.

Any insight you can provide is appreciated.

Let me know where to email the schematics.

Thank you for your time and attention towards resolving this issue.

Kishen