Other Parts Discussed in Thread: DS32EL0124

Hi,

I would like to ask you a question about an interface between "Sub-LVDS" and this device.

My customer is planning to connect FPGA out which is "Sub-LVDS" with DS32EL0421.

Is it possible to connect "Sub-LVDS" with DS32EL0421 dilectly?

The main issues to connect seem to be needed to consider are as follows.

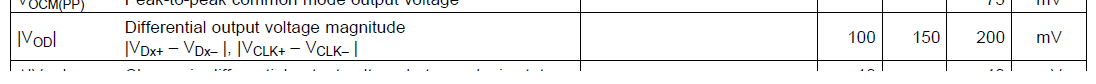

I1) Sub-LVDS output is +/-75mV but DS32EL0421 is +/-100mV

I2) Sub-LVDS needs +/-1% accuracy for external terminal resister, but DS32EL0421 has +/-15% internal resister.

The detail specification of Sub-LVDS is as below.

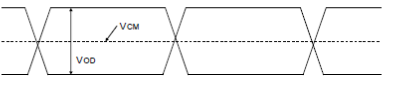

| LVDS OUTPUT Spec | |||||

| Item | simbol | Min | TYP | Max | |

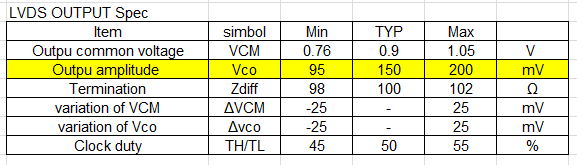

| Outpu common voltage | VCM | 0.76 | 0.9 | 1.05 | V |

| Outpu amplitude | Vco | 95 | 150 | 200 | mV |

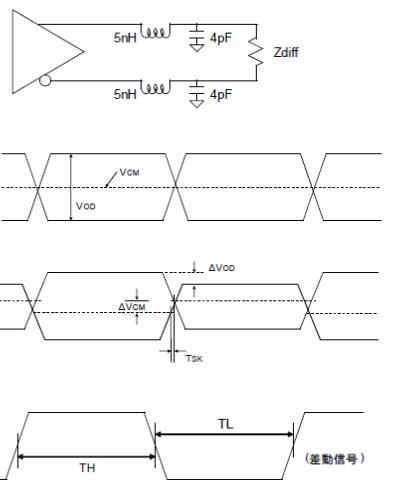

| Termination | Zdiff | 98 | 100 | 102 | Ω |

| variation of VCM | ΔVCM | -25 | - | 25 | mV |

| variation of Vco | Δvco | -25 | - | 25 | mV |

| Clock duty | TH/TL | 45 | 50 | 55 | % |

| LVDS AC Spec | |||||

| Item | simbol | Min | TYP | Max | |

| Internal clock | - | - | 594 | MHz | |

| Set up time | Tlvdssh | 420 | - | - | ps |

| Hold time | Tlvdshd | 420 | - | - | ps |

(LVDS out clock = 297MHz)

About I1), If it is not possible to connect directly, could you advise me how to realize to connect?

Or could you tell me another apropriate device to connect?

About I2), Could you tell me the way to use external terminal resister instead of internal one?

Or is it possible to provide me +/-1% device?

Thank you very much for your support in advance.

Best Regards,