Other Parts Discussed in Thread: TCA4311

Hi,

My customer is evaluating the TCA4311A schematic as follows.

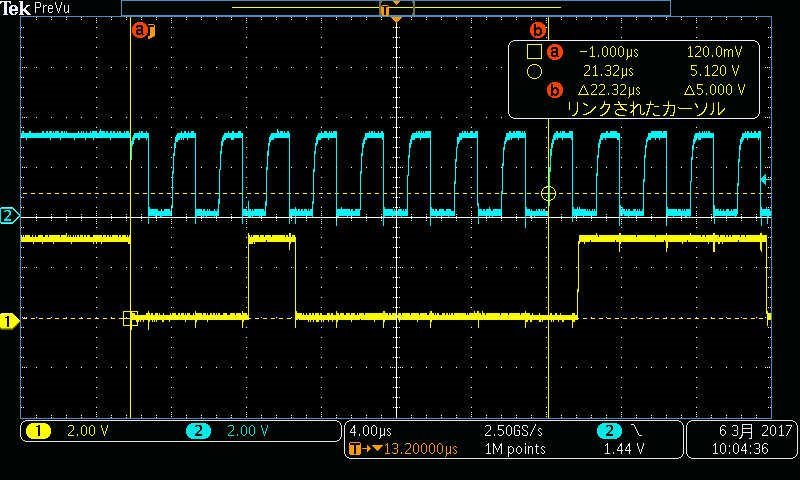

The SDIN is distorted when the TCA4311A is connected as follows.

Is this correct working?

Best Regards,

Kuramochi

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Kuramochi-san,

I will look at this today and get back to you.

-Francis Houde

Hi Houde-san,

Thank you for you support.

OK, I confirm your questions for my customer.

1) What is the problem that the customer is seeing?

The problem is the distortion inside the following red rectangle.

Do you think that this symptom depends on the TCA4311A or customer's application?

Best Regards,

Kuramochi

Hi Houde-san,

I add the information I get.

2) Where in the circuit are they doing the insertion? Is it board to board or a wire harness?

→Wire harness

Is the problem they are seeing during hotplug or after everything is stabilized and connected?

→everytime

3) From what I can see it seems like the SDA is working ok, my question is more about what is going on with your SCL?

You have a wide pulse in the middle, what does the SCLin look like at the same time.

→Repeat Start Condition.

Have them do recording of waveforms of both sides of the device (SCLin, SCLout, SDAin, and SDAout) when they see problems.

→I attach the waveforms.

4)When I looked at the waveform where the TCA4311A isn’t connected, it looks funny to me. I assume Ch 2 (blue) is SCL, and it looks like an open drain signal. Channel 1 (yellow), it looks like a pushpull output. Can you verify what is going on there? Channel 1 and 2 have significantly different rise times, which implies either different pull up resistors or very different capacitive loading.

→The capacitance of protection device is 4pF(typ).

Best Regards,

Kuramochi

Hello Kuramochi-san,

I am at a bit of a loss as to why you are seeing SDAout with the severely deformed waveform. I think I need for information about their setup.

You told me they were using a wire harness, but I need more information about the harness. What is type of wire? What is the capacitance/cm? length of wire? This will give me an estimate of capacitive loading. The gauge of wire will tell me the inductance/cm. If the wiring harness is long then we might be seeing reflections due Rise Time Accelerators (RTA). I don’t think that is the issue, but I want to make sure. The below waveform seems to have a very large amount of capacitance that the RTA can’t handle. You may need to significantly increase the pullup resistors or look at using stronger buffers that can handle the stronger pullups. Also, how are they capturing this waveform? It looks like a sloppy probe setup with lots of noise on the measurement.

2. What is the part number of the TVS? I want to see the information about standoff voltage and leakage current. I am worried that they TVS is conducted when you aren’t expecting. This might make it look, impedance wise, like a large capacitive load.

3. You have only given me a hand drawn circuit, is there a schematic? I want to know if there is anything else on both sides of the buffer? Are there other buffers? Or just devices? I want to make sure there isn’t two devices fighting each other, like having two buffers with different static voltage offsets connected to the same node.

4. I still don’t understand why the wavefom below has two significant different rise times? You said this was “the waveforms when TCA4311A is not connected”, does that mean it was bypassed by shorting SDA/SCLin and SDA/SCLout or the hardness was removed? Please clarify.

5. Is their system no communicating properly? What is the problem? Just that they don’t like the waveform?

5. Is their system no communicating properly? What is the problem? Just that they don’t like the waveform?

6. What is the goal of the design? What is the application? You might be using the wrong part.

It is difficult for me to debug their system remotely. If there is a significant problem then I am more than willing to receive a shipped unit to debug in the lab.

-Francis Houde

Kuramochi-san,

1) Do we have any capacitance values for the harness????

2) It looks like the zener diodes are low capacitance and the standoff voltage is high enough that there is no meaningful current conducting in the zener at the voltages seen in the application. That's good.

3) Is this a statement? Are there other buffer's other than TCA4311A? Yes or No? If Yes, what is their part number and how is it connected to the TCA4311?

4) Have they verified that the different rise times still meet the I2C standards for rise time?

5)The distortion is due to the very large ( I am guessing) capacitance on the SDA/SCL lines due to harness and how it interacts with our device, TCA4311A. The TCA4311A has Rise Time Accelerators (RTAs) which turn on as the bus is released and the pull-up resistor starts to raise the voltage at that node. As the voltage rises above 0.6V a 2mA constant current source is switched in between the node and Vcc, which means it is in parallel with pull-up resistors. Note that there could be inductance between the TCA4311A's RTA and the pullup on the node which could be on either side of the harness. That could account for the distortion too. The RTA is only on for a short period of time and once it is turned off the node continues to rise towards the voltage rail, Vcc. The hope is that the RTA is on long enough to raise the voltage node to Vcc, but if the node has too much capacitance than the RTA turns OFF before it has reached Vcc and only the pull-up resistor has the job of raising the node to Vcc. Thus we see the different stages of when the node is release from 0V to rise to Vcc. I would like to have a system level diagram that includes master device, pull-up resistor locations and values, harness size and parasitic information, TCA4311A location, and information about everything is connected together in a real life.

I explained how the RTA work but my guess is that the parasitic connections and properties affect the signal and how it looks. Can you tell me where you are taking the waveforms too. That might also explain why it looks the way it does.

-Francis Houde