Hi team,

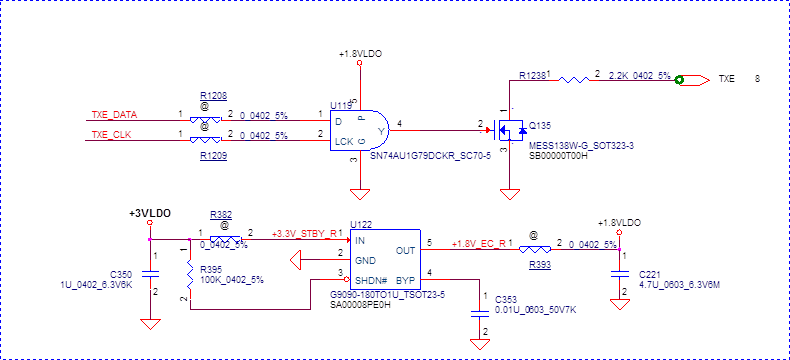

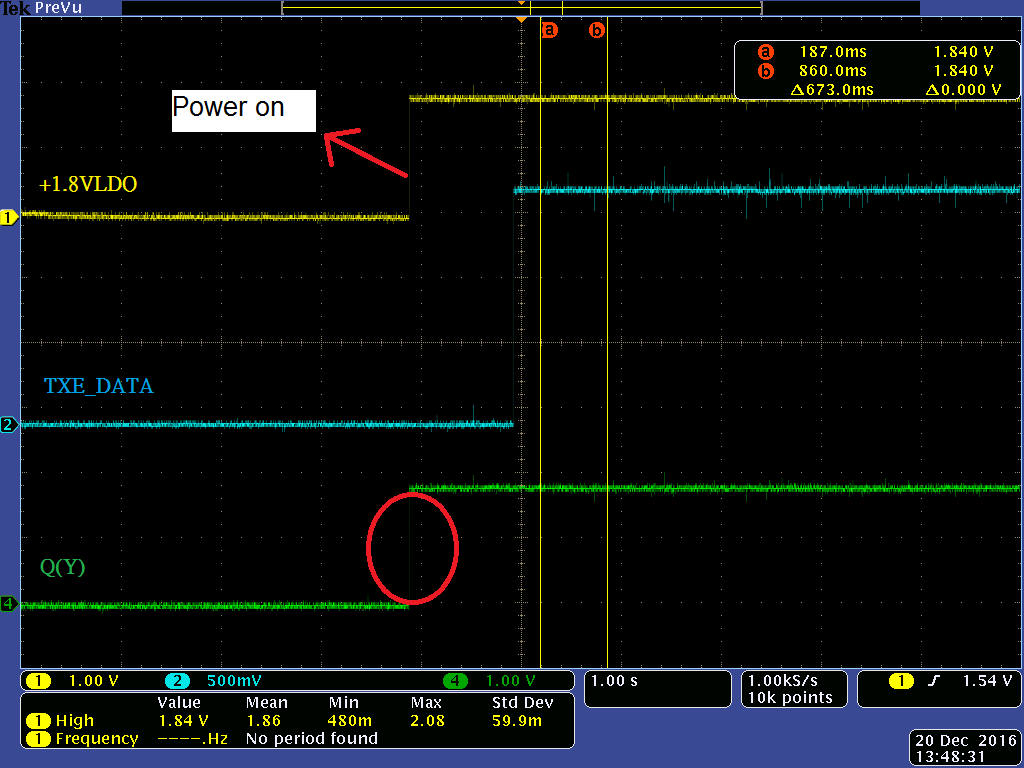

One of our customers is facing a problem related to the behavior of OUPUT Q. The customer has the circuit like the schematic below. They found out that when the IC is powered on, the OUTPUT Q would go high level befroe D pin goes to High level. Please refer to the wavefore below. However, if a probe is placing on the CLK path, the behavior of OUTPUT Q does no have this kind of behavior. Do you know what is causing this problem? Or does the customer need to add another circuirty to prevent it? Thanks for your support and time.

Leroy Song