Hi,

I'm currently developing a software for the MSP430F5510. It worked fine with my development PCB for months, but as soon as I tried it on another one, I got very strange issues. My software is writing text to a display with a built-in font, and I'd sometimes get missing pixels, or the text "dEbug" or "debuf" instead of "debug".

I then simplified my code until I arrived at this:

#include <msp430.h>

#include <string.h>

#include "driverlib/MSP430F5xx_6xx/ucs.h"

static const uint16_t flash_data[] = {

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF,

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF,

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF,

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF,

};

static volatile uint16_t ram_data[] = {

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF,

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF,

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF,

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF,

};

void main(void)

{

volatile uint32_t cnt = 0;

static const uint32_t mclk = 25000000;

WDTCTL = WDTPW | WDTHOLD;

UCS_clockSignalInit(UCS_FLLREF, UCS_REFOCLK_SELECT, UCS_CLOCK_DIVIDER_1);

UCS_initFLLSettle(mclk/1000, mclk/32768);

while (1) {

if (memcmp(&flash_data, (void*)&ram_data, sizeof(flash_data)) != 0) {

_op_code(0x4343); # Software breakpoint

}

cnt++;

}

}

My code sometimes stops on the software breakpoint, so it seems sometimes the flash gets read incorrectly. Most of the times this happens very soon after the program starts (cnt <= 50), but sometimes it takes a lot longer (cnt = some millions). Then after the next reset it immediately happens again.

Some observations I made so far:

- It does not seem to happen when the clock is 24MHz instead of 25MHz

- It does not seem to happen on 2 of 4 prints I tested

- When I use single values rather than arrays, it happens more seldom. If I use != instead of memcmp to compare them, it doesn't seem to happen (maybe it gets optimized away though?).

- Optimisation level doesn't seem to make a difference

- Inserting an ~1s delay before and after setting the clock doesn't make a difference

- It seems it's always an 1 bit read as 0, i.e. I can't reproduce it if the data is 0x00 instead of 0xFF

CCSv5 project with the above minimal example: 3326.corruption_test.zip

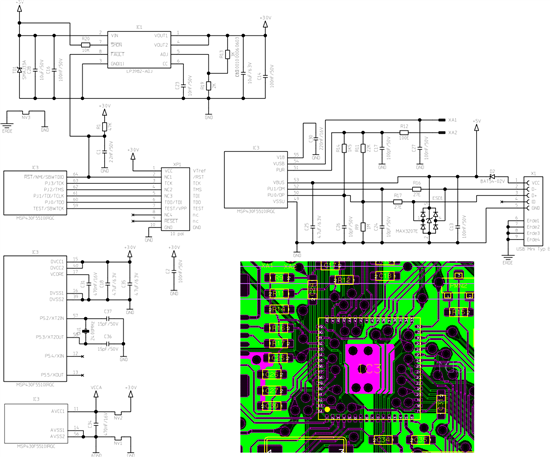

The related parts of the schematics and layout look like this:

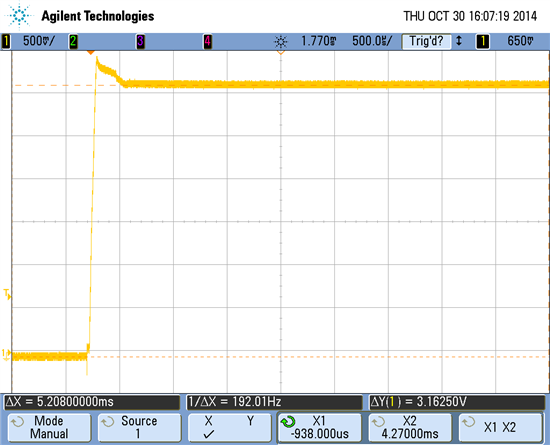

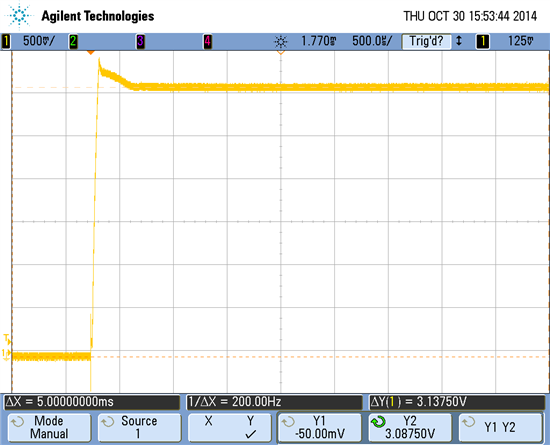

The supply voltage looks good for both unaffected and affected prints.

Good:

Bad:

I've seen TIs document about the flash corruption issue (slaa471), but they mention the MSP430F5510 is unaffected, and the kind of corruption doesn't seem to be the one I'm seeing.

I've also not seen anything related in the errata (slaz301j), except "Corrupted flash read when SVM low-side flag is triggered" which doesn't seem to be my issue. The chip revision is C, for both affected and unaffected prints.

Any help would be appreciated, I really have no idea what to try anymore. Thanks!