Tool/software: TI-RTOS

Hello All,

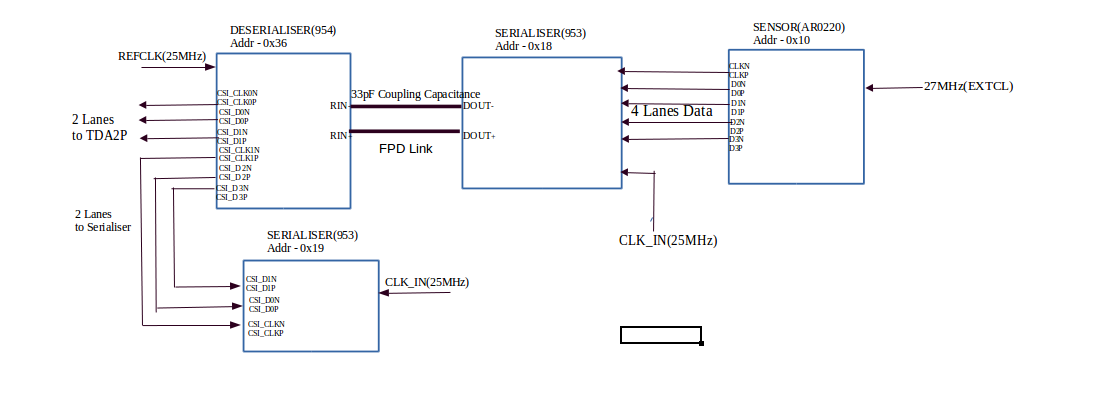

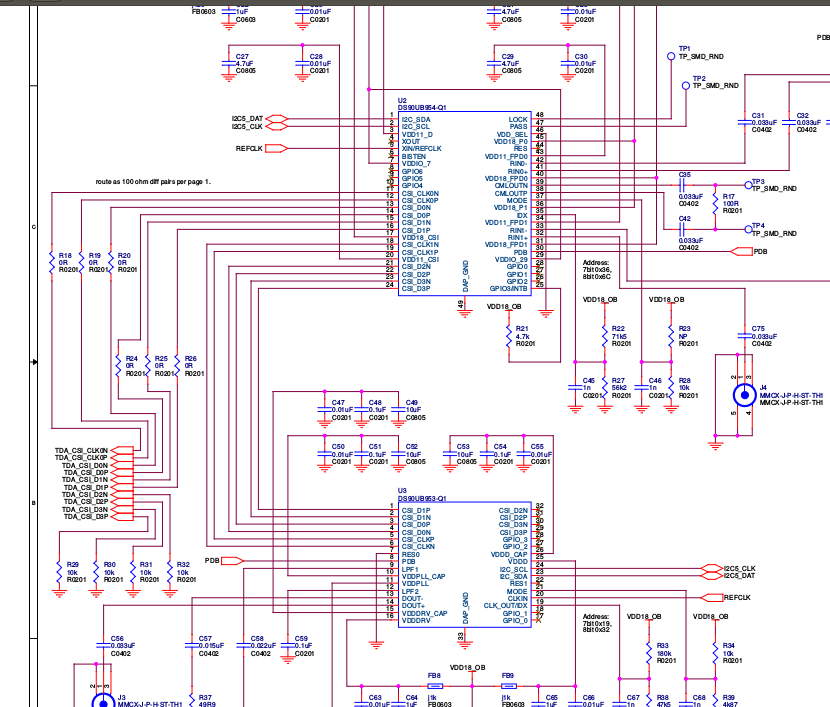

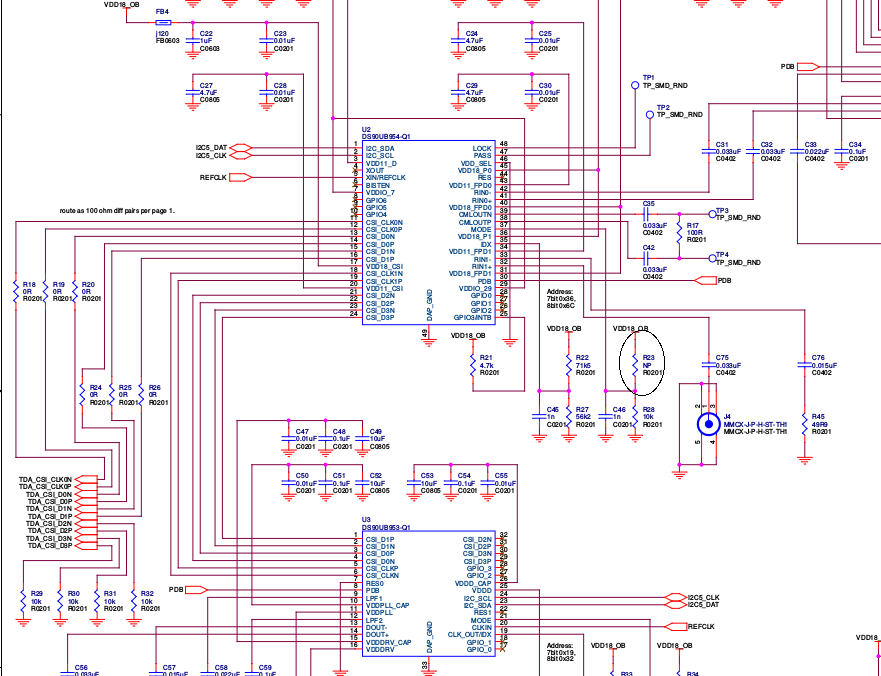

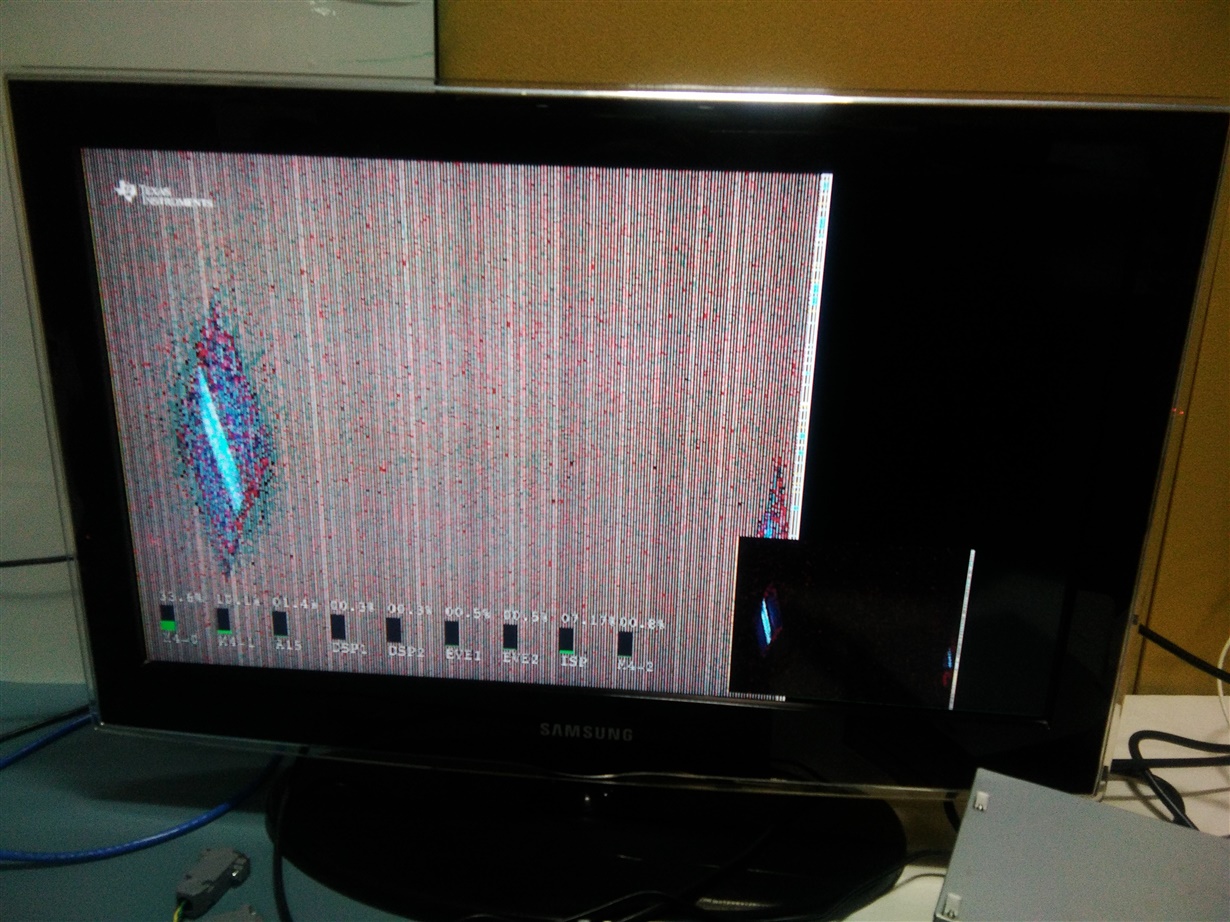

We are working with AR0220 camera sensor + UB953/UB954 SERDES on custom TDA2P board.

Earlier we were working on TDA2Px-EVM with AR0220 and SERDES which was working. We have taken the same working configurations on custom board.

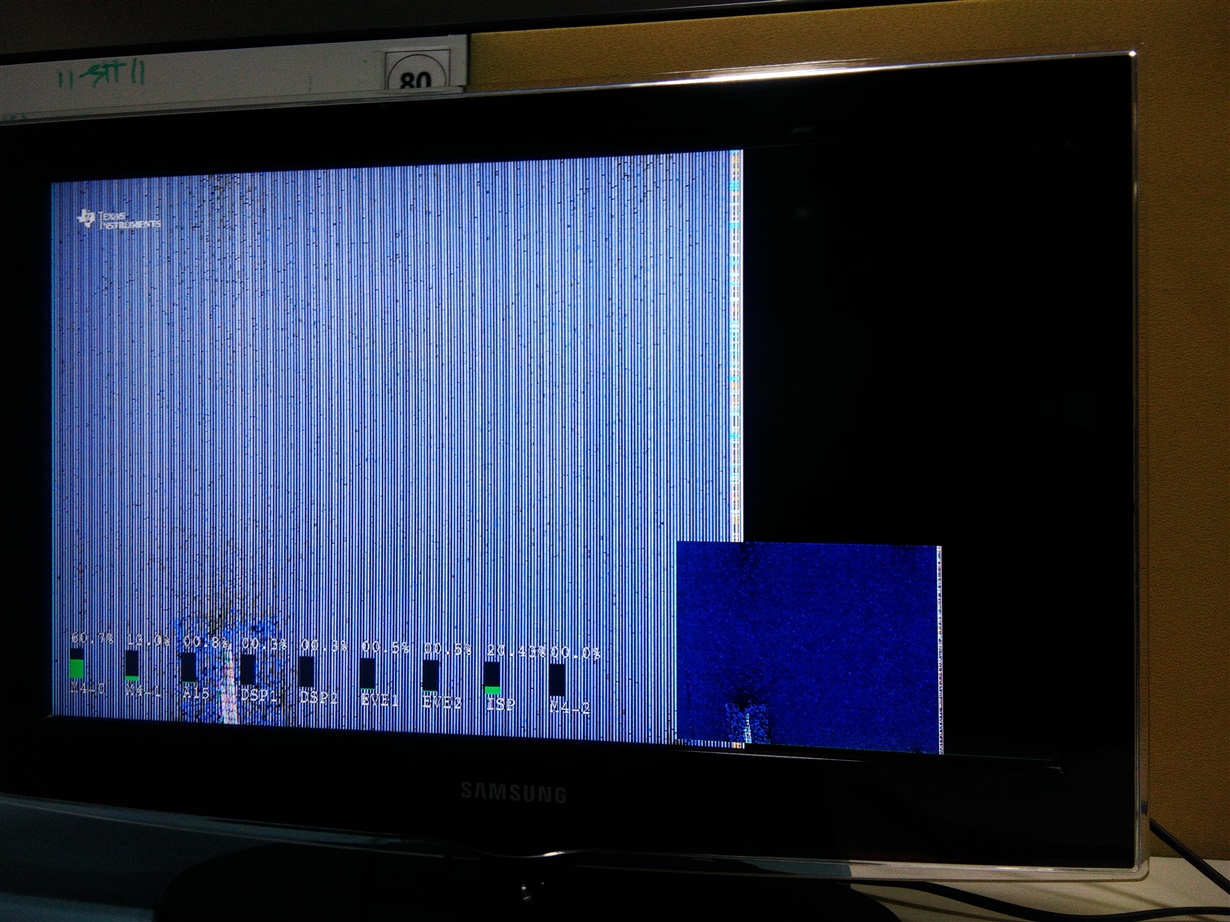

But we are getting I2C bust busy error as shown below,

"

Serilaizer # 0 has I2CAddr 74 !!!

Setting GPIO RST Pin

GPIO RST Pin setting DONE

src/bsp_deviceI2c.c @ Line 1567:

Bus busy detected recover I2C bus !!!

src/bsp_deviceI2c.c @ Line 667:

I2C4: DEV 0x40: ERROR !!!

I2C4: Error timeout 5074 ms!!!

Assertion @ Line: 507 in vision_sdk/apps/src/rtos/iss/src/common/app_util_iss.c!

"

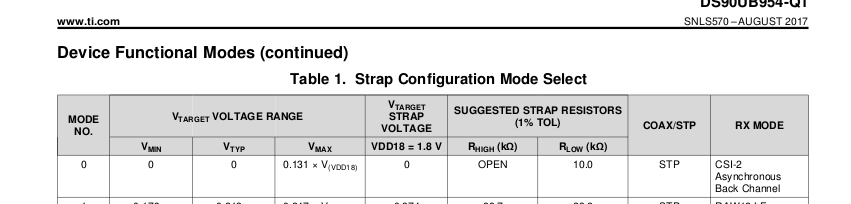

We are using below settings in file "\apps\src\rtos\iss\src\sensor\iss_sensor_tda2px.c",

"

{SENSOR_AR0220,

{

4u, /* I2C Instance id for the sensor */

{0x40}, /* I2C Alias Address of the sensor */

{0x74}, /* I2C Alias Address of the serializer */

TRUE, /* Flag for single/multi channel sensor config */

SYSTEM_VIFW_4LANES, /* Interface width */

SYSTEM_VIFM_SCH_CSI2, /* Video Interface mode - Single channel capture via CSI2 interface */

SYSTEM_CSI2_RAW12, /* Input CSI2 Data Format */

0, /* Virtual Channel Id */

0, /* Is CSI Enable Required in UB954 */

{TRUE /* isCplxCfgValid */,

{{FALSE, 1}, /* Clock Lane */

{FALSE, 2}, /* data1Lane */

{FALSE, 3}, /* data2Lane */

{FALSE, 4}, /* data3Lane*/

{FALSE, 5}},/* data4Lane */

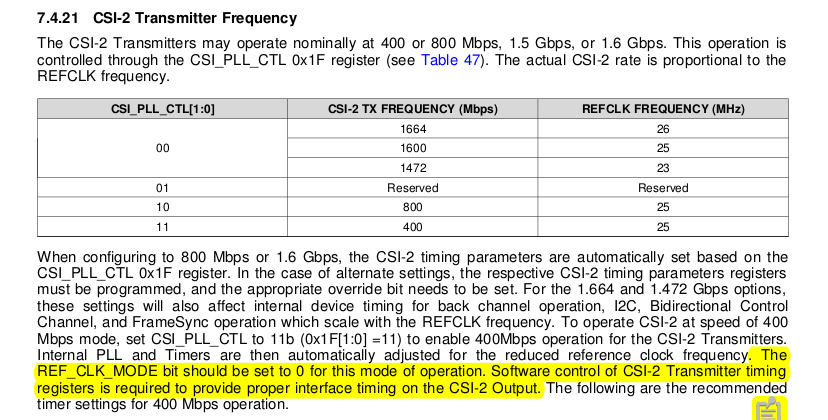

800 /* csi2PhyClk */ },

FVID2_VID_SENSOR_AR0220_DRV, /* sensorDrvId */

FALSE, /* sensorBroadcast */

FALSE, /* enableFsin */

{0x36} /* I2C address of deserializer */

}}

"

Can anyone suggest how do we solve I2C bus busy error.

Regards,

Abhay