高速アンプを使って設計する際には、共通の仕様に精通し、考え方をある程度理解しておくことが重要です。この技術記事では、ゲイン帯域幅積(GBW)が50MHz以上を高速オペアンプとしますが、それ以下の速度のデバイスにもここで紹介する考え方が当てはまる場合もあります。高速アンプを用いる場合に設計者がよく抱く疑問をいくつか紹介していきます。

Q:一部の高速オペアンプの仕様に最小ゲインが規定されているのはなぜですか?

A:不完全補償型オペアンプには閉ループの最小ゲイン安定仕様がありますが、ユニティ・ゲイン安定アンプと比べて不完全補償型オペアンプは、消費電流が同じ場合にGBWが広くノイズが低くなります。

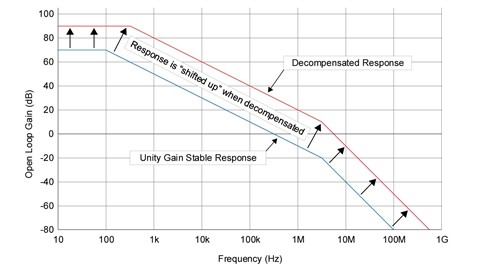

「不完全補償型」とは単純に、Aol(開ループ・ゲイン)の応答曲線上に0dBより上の2番目の極があることを意味します。この2番目の極によって、アンプの安定性を保証するのに必要な最小ゲインも定まります。図1のように、Aol曲線が「上にずらされた」と考えてください。Aolが増加することで、帯域幅が広がります。

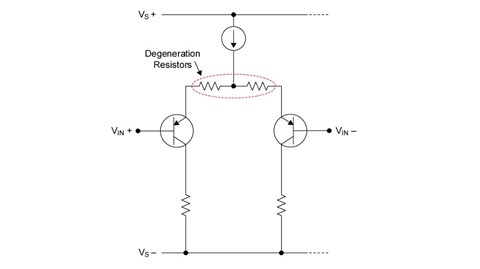

図2に示すように、アンプの入力ペアの縮退抵抗を小さくすると、Aolが増加します。縮退抵抗の減少によって、アンプのノイズも低減されます。

『OPA858』と『OPA859』は、それぞれ不完全補償型アンプとユニティ・ゲイン安定アンプの例です。表1のように、消費電流が同じ場合、『OPA858』の方が帯域幅が広く、低ノイズです。

|

|

(不完全補償型) |

(ユニティ・ゲイン安定) |

|

静止電流(IQ) |

20.5 mA |

20.5 mA |

|

ゲイン帯域幅(GBW) |

5,500 MHz |

900 MHz |

|

電圧ノイズ(Vn) |

2.5 nV/√Hz |

3.3 nV/√Hz |

|

スルー・レート |

2,000 V/μs |

1,150 V/μs |

|

最小ゲイン(Acl) |

7 V/V |

1 V/V |

表1:不完全補償型アンプとユニティ・ゲイン安定アンプの比較

帯域幅が広がりノイズが低減することのほかに、不完全補償型アーキテクチャではスルー・レートも高くなります。全体として、ユニティ・ゲインを諦めて最小ゲイン要件を満たせる場合に、最小ゲイン仕様によって、利用できる性能の面でトレードオフが生まれます。最小ゲイン仕様を容易に満たせるアプリケーションの例として、シャント抵抗の両端の電圧を測定する電流センシング回路、シグナル・チェーンのゲイン段、トランスインピーダンス回路などがあります。

Q:電流帰還アンプとは何ですか?

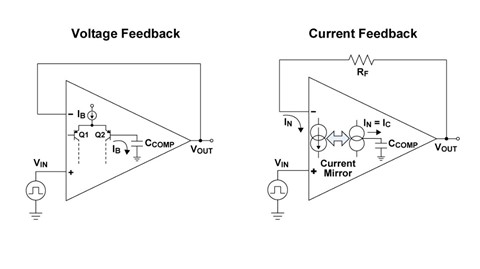

A:電流帰還アンプとは、出力信号の一部を電流として帰還させてアンプを制御するオペアンプのことです。電流帰還アンプは、電圧の形の帰還に依存する電圧帰還アンプとは異なります。多くの設計者は、ほとんどの電子工学履修過程で重視されている、より一般的な電圧帰還アーキテクチャには慣れているでしょう。

図3は、基本的な入力段での電圧帰還と電流帰還のアンプ・アーキテクチャの比較です。ここでは、電圧帰還アンプを電圧で制御された電圧源としてモデル化し、電流帰還アンプを電流で制御された電圧源としてモデル化しています。

どちらのアーキテクチャも、負帰還回路の誤差増幅器として使われてはいますが、必要とする帰還のタイプが異なります。例えば、反転と非反転のゲイン構成には、どちらのタイプのアンプも使用できます。電流帰還アーキテクチャの利点として1つ明らかなのが、帯域幅がゲインに依存しないことです。電圧帰還アーキテクチャでは逆に、式1でわかるようにゲインが増加すると帯域幅が減少します。

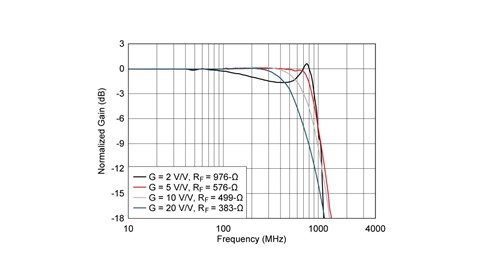

電流帰還アーキテクチャでは、図4のようにゲインに関わらず帯域幅はほぼ一定です。このグラフは『THS3491』データシートのものです。

表2に、電圧帰還アンプと電流帰還アンプの主な違いを比較しています。

| 電圧帰還アンプ | 電流帰還アンプ | |

| 帯域幅 | 帯域幅はゲインにより変化する | どのゲインでも帯域幅はほぼ一定 |

| DC精度 | 高い | 低い |

| 出力スイング | レール・ツー・レール出力のオプションが多い | 出力にはより大きいヘッドルームが必要 |

| 歪み | 低周波数歪みが良好 | 高周波数歪みが良好 |

| スルー・レート | 限定されたスルー・レート | 高い全出力帯域幅を可能にする非常に高いスルー・レート |

| ゲイン安定性 | 不完全補償型アンプの最小安定ゲインに制限 | 帰還トランスインピーダンスが一定のままなら、どのゲインでも安定 |

| ノイズ | 入力換算電圧ノイズおよび電流ノイズが低い | 入力換算電流ノイズが高い(反転入力と非反転入力とで等しくない) |

| 代表的なアプリケーション |

DCの精度が必要なアプリケーション

|

D/Aコンバータ・インターフェイス 出力ドライバ 高速ADCインターフェイス サレン・キー型フィルタ |

表2:電圧帰還アンプと電流帰還アンプのアプリケーションの比較

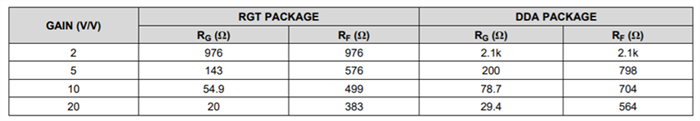

電流帰還アンプは、帰還パスに抵抗を入れずに使用することは考えられていないことに注意してください。電流帰還アンプのデータシートには、推奨するRFの規定値が記載されています。ユニティ・ゲインであってもRFの値でアンプの補償が決まるため、この値が重要です。図4と同様に、表3は『THS3491』データシートのものです。

表3:『THS3491』データシートのRFの推奨値の例

電圧帰還と電流帰還の2つのアーキテクチャの違いについて詳しくは、「電圧帰還アンプと電流帰還アンプを理解する」(英語)をご覧ください。TIプレシジョン・ラボのオンライン・トレーニング・ビデオを視聴することでも、電流帰還アーキテクチャについて詳しく知ることができます。

Q:ブレッドボードに設置したときに高速アンプが発振する原因は何ですか?

A:一般的に言うと、パッケージのリードのインダクタンスと、ブレッドボードの容量とインダクタンスが、高速アンプの発振を引き起こしていると考えられます。同様に、高速オペアンプを用いた設計の際にも、プリント基板(PCB)の容量とインダクタンスを最小限に抑えることが重要です。50MHzの『OPA607』のように、高速アンプのGBW周波数範囲の下端に位置するデバイスでも、この種の基板レベルでの設計上の考慮が必要です。

以下の方法で、高速レイアウト設計を最適化することができます。

- パターン長を最小限にする

パターン長を最小限にすることで、余分な容量とインダクタンスが削減されます。 - ソリッドなグランド・プレーンを使用する

高速設計では、細かく分割されたプレーンよりもソリッドなグランド・プレーンの方が適しています。 - 信号パターンの下のグランド・プレーンを切り抜く

デバイスの入力および出力の下のグランド・プレーン・メタルを除去することで、影響を受けやすいノードの寄生容量の低減になります。 - 信号パス上のビアの数を最小限にする

ビアによってインダクタンスが増加するため、100MHzを超える周波数では信号忠実度に問題が出る可能性があります。信号忠実度の問題を緩和するには、重要な信号をアンプと同じ層に配線してビアを無くします。 - 電流のリターン・パスを最適化する

信号パターンのレイアウト設計では、信号ループの総面積を最小限にする必要があります。それにより、インダクタンスが抑えられます。 - バイパス・コンデンサを適切に配置・配線する

バイパス・コンデンサをできるだけアンプに近く、基板上で同じ面に配置します。パターン幅を広くし、ビアを、コンデンサとアンプの間ではなく、バイパス・コンデンサに配線してからアンプに配線します。 - 抵抗を適切に配置する

ゲイン設定、帰還、直列出力のそれぞれの抵抗は、デバイス・ピンの近くに配置して、基板の寄生成分を最小限に抑えるようにします。

高速オペアンプの性能を評価するときは、特定のデバイス用に指定された評価モジュールを使用することを推奨します。これらの基板は、優れた高速基板レイアウト設計を実証し、またSMAコネクタの使用により、高忠実度でインピーダンス制御された信号パスを維持します。高速基板レイアウトの実際について詳しくは、「高速PCBのレイアウト技術」(英語)をご覧ください。

総合的には、高速オペアンプの動作は、低速のオペアンプとほぼ同じです。設計のほんのわずかな違いを考慮することで、速度と性能のメリットのすべてをシステムに活かすことができます。

※すべての登録商標および商標はそれぞれの所有者に帰属します。

※上記の記事はこちらの技術記事(2020年7月17日)より翻訳転載されました。

※ご質問はE2E Support Forumにお願い致します。