各種ファクトリ オートメーション機器、たとえばセンサ、アクチュエータ、ドライバ、プログラマブル ロジック コントローラ (PLC) は、EtherCAT、Profinet、イーサネット産業用プロトコル (EtherNet/IP)、Sercos のような各種産業用イーサネット プロトコルをサポートしています。これらのプロトコルは、ハードウェア プラットフォームに異なるソフトウェア イメージをロードして切り替えることが可能です。

マルチプロトコルの産業用イーサネット システムを使用すると、単一のプリント基板 (PCB) を製作するだけで済みます。そのため、部品表 (BOM) コストが低下し、ハードウェア開発サイクルでの製造コストを削減できるほか、全体の開発期間の短縮にもつながります。メーカー各社は、多様な産業用イーサネット プロトコルに対応したファクトリ オートメーション向けに、デジタル入力モジュールやサーボ ドライブのような各種フィールド デバイスを提供しています。

TI のプログラマブル リアルタイム ユニット産業用通信サブシステム (PRU-ICSS) などのアーキテクチャは、フィールド デバイスで 1,000Mbps の速度をサポートすることができます。そのためには特に、新しい TSN (Time-Sensitive Networking) プロトコルが使用されます。

産業用イーサネット システムのアーキテクチャ

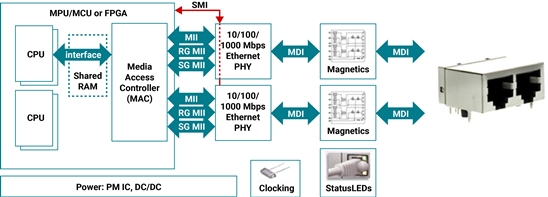

図 1 に、PLC や他のフィールド デバイスとの間でプロセス データを交換する産業用イーサネット フィールド デバイス内の各種主要部品を示します。2 個のイーサネット ポートはラインまたはリング形状のイーサネット トポロジをサポートしています。つまり、イーサネット スイッチなしで、複数のイーサネット ケーブルを使用して PLC を一連のフィールド デバイスに接続することができます。

図 1:産業用イーサネット フィールド デバイスのシステム ブロック図

RJ45 コネクタから各種磁気素子までの間を MDI (Medium Dependent Interface) で接続します。これにより、電気的な絶縁バリアを確立したうえで他のデバイスに接続し、信号を伝達することができます。その後、イーサネット フレームがイーサネット物理レイヤ (PHY) トランシーバに流れます。

PHY は、イーサネット フレームをアナログ信号からデジタル信号へ (レシーバ) およびデジタル信号からアナログ信号へ (トランスミッタ) 変換し、MII (Media Independent Interface) 経由でデジタル ビットストリームを出力します。MII としては、RGMII (Reduced Gigabit Media Independent Interface) や SGMII (Serial Gigabit Media Independent Interface) なども使用されます。

メディア アクセス コントローラ (MAC) と同様、PHY は産業用イーサネットにとって重要な役割を果たします。MDI に応じて、PHY は異なるペア数 (T1 シングルペア イーサネット向けには 1 ペア、100Mbps イーサネット向けには 2 ペア、1,000Mbps イーサネット向けには 4 ペア) を内蔵している銅線メディアをサポートする必要があります。いくつかの産業用イーサネット ネットワークは、ファイバもサポートしています。ファイバには、条件の厳しい産業用環境で電磁適合性 (EMC) や電磁干渉 (EMI) に由来する外乱に対する回復力が高いという特長があります。

次に、一連のイーサネット バイトで構成された MII ストリームを MAC に渡します。MAC は産業用イーサネット プロトコルの処理を担当し、マルチプロトコル産業用イーサネットのサポートにおいて重要な機能ブロックの 1 つです。

各産業用イーサネット プロトコルは、プロセス データを抽出および挿入する際の産業用イーサネット フレームの処理方法がそれぞれ異なるため、プロトコルごとに MAC の処理方式を変更する必要があります。MAC のような特定用途向けの IC (ASIC) ソリューションは通常、単一のプロトコル向けに固定されており、マルチプロトコルに対応する能力はありません。一方、マルチプロトコル対応の MAC はイーサネット フレームのさまざまな処理方式をサポートする必要があります。たとえば、オンザフライ (即時処理)、カット スルー (分割形式)、フレーム プリエンプション (フレームの事前処理)、ストア アンド フォワード (いったん蓄積した後に転送) などです。

MAC は PLC から受け取ったプロセス データを、インターフェイスを経由して中央演算装置 (CPU) が使用できるようにします。MAC が物理的に独立したデバイスである場合、このインターフェイスは低速 (SPI:Serial Peripheral Interface、I2C、またはメモリ マップ型外部バス) です。一方、MAC と CPU が統合型である場合、共有の高速メモリがインターフェイスを処理し、MAC と CPU の間でプロセス データを同期します。

CPU はさまざまなタスクを実行します。各産業用イーサネット プロトコルは、プロセス データを交換できるように、MAC と双方向通信を行うソフトウェア スタックを必要とします。フィールド デバイスはこのプロセス データを使用して、デジタル入出力の制御、または、サーボ ドライブの速度と方向の制御を行います。

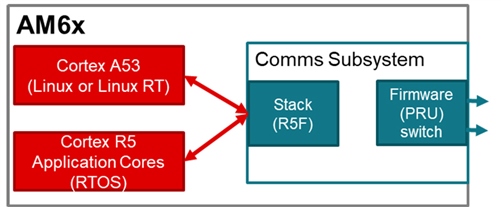

システムが複数の CPU を搭載している場合、一般的な手法はワークロードを分割することです。この場合、産業用イーサネット スタックは専用の CPU で実行され、産業用アプリケーションは別の CPU 上で動作します。

複数の CPU コアを使用して、複数の種類のオペレーティング システム (OS) を動作させることもできます。たとえば、Linux やリアルタイム Linux のようなハイレベル OS (HLOS)、または Free-RTOS や no-OS のようなリアルタイム OS (RTOS) などです。

マルチプロトコル産業用イーサネットに対応する TI Sitara ファミリの各種ソリューションと TI の各種イーサネット PHY

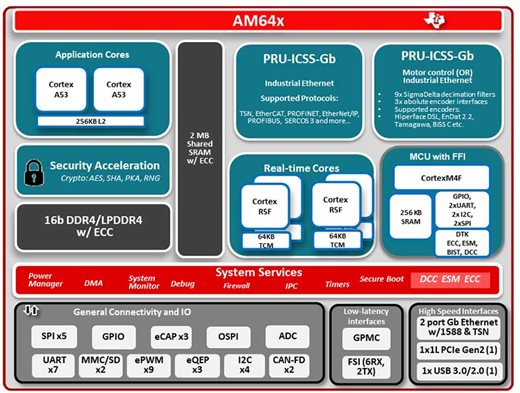

Sitara プロセッサ ファミリは、内蔵の PRU-ICSS ペリフェラルを使用して、プログラマブル MAC をサポートします。PRU は、実行時に各種産業用プロトコルのファームウェアをロードします。図 2 に示す Sitara AM6442 や、AM2434 と AM2434 は、TSN のような各種 1,000Mbps プロトコルをサポートします。また、PRU-ICSS は、1 つの標準イーサネット MAC として、あるいは 2 ポートのイーサネット スイッチとしても動作します。

図 2:マルチプロトコル産業用イーサネットをサポートする、Sitara AM6442 プロセッサ ソリューションと PRU-ICSS の組み合わせ

Sitara プロセッサ ファミリには PRU-ICSS の複数のインスタンスをサポートする能力があります。その結果、位置エンコーダ (EnDAT 2.2、HIPERFACE デジタル サーボ リンク [DSL]、双方向シリアル同期 [BiSS])、パルス幅変調 (PWM)、外部の絶縁型 A/D コンバータに適したデルタ シグマ デシメーション フィルタなどの産業用ペリフェラルを実現できます。サーボ ドライブは、この種のペリフェラルを使用します。

また、Sitara プロセッサは、ADC、SPI、I2C、汎用メモリ コントローラなど、産業用アプリケーションで使用される多様な機能を内蔵しています。このシステム オン チップ (SoC) は、MAC と CPU の間でプロセス データを交換するための内部共有メモリも搭載しています。

図 3 に示すように、Sitara プロセッサ ファミリは、HLOS 向けの複数の Arm® Cortex®-A53 コアや、RTOS またはベアメタル アプリケーション向けの複数の Arm Cortex-R5F コア、産業用イーサネット MAC 向けの PRU-ICSS を搭載しています。

図 3:RTOS、HLOS、ファームウェアを活用するマルチコア処理

プログラマブル MAC アプローチの統合により、シングルチップ構成のアプリケーション プロセッサを使用して、マルチプロトコル産業用イーサネットが必要とするさまざまなフレーム処理方式をサポートできます。高速内部メモリ インターフェイスを経由して、プロセッサと MAC の間でのプロセス データの高速な交換を実行できます。また、このファミリはスケーラブルな各種プロセッサ コアも取り揃えています。

TI はイーサネット PHY ソリューションを搭載した Sitara プロセッサ ファミリ向けに、DP83867 または DP83869 どちらかのイーサネット PHY トランシーバを採用した評価基板 (EVM) を提供しています。

参考情報

- AM64x と AM24x 向けのソフトウェア開発キット (SDK) に含まれる 100Mbps および 1,000Mbps イーサネット用の各種産業用プロトコルの詳細をご確認ください。

- Sitara プロセッサに対応する PRU-ICSS 産業用ソフトウェアおよび利用可能な統合型産業用プロトコルの詳細をご確認ください。

- TI の産業用通信アカデミーをご覧ください。

- TI の Sitara AM64x 評価基板 (EVM) をご確認ください。

- AM243x Arm ベース マイコン向け、汎用 LaunchPad 開発キットをご注文いただけます。