この技術記事はDan Toothとの共著です。

設計者として、「今度の設計では、2倍の量の部品を半分のスペースに追加コストなしで収めないといけない」といったことはよくあるかもしれません。そのために、最小のPOL(ポイント・オブ・ロード)レギュレータを選択し、費用対効果が最も優れたパッシブ部品を使って、できる限り詰め込んだレイアウトを作りあげました。ここまではいいでしょう。ところが、重要な電源レールの出力リップルを見ると、予想したものと違います。どうなっているのでしょうか。

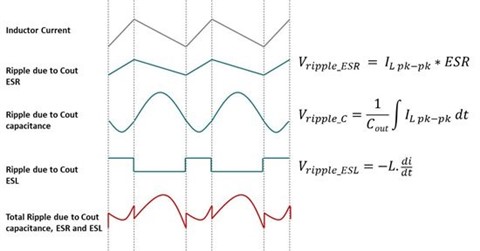

それではまず、降圧DC/DCレギュレータの出力リップルが何で構成されているかを理解するところから始めましょう。出力リップルは合成波形です。従来から、図1に示す3つの主要な要素のみが考慮されてきました。

- インダクタの電流上昇が出力コンデンサの等価直列抵抗(ESR)に加わることで生じる三角波。22µF X5Rセラミック・コンデンサのESRは2mΩしかないことがあります。インダクタのピーク・ツー・ピーク電流リップルが1Aだとすると、ESRのリップルは2mVです(コンデンサを複数並列で使用している場合はこれより低くなります)。

- 出力容量に起因する疑似正弦波成分。上の項目と同じ出力コンデンサとリップル電流の場合、容量性リップル電圧はおよそ8mVになります(出力コンデンサを複数並列で使用している場合はこれより低くなります)。

- 出力コンデンサの等価直列インダクタンス(ESL)で生じる方形波成分。22µF X5Rコンデンサだと、およそ0.5nHのESLから約2mVのリップルが生じます。

図1:典型的な出力リップル波形

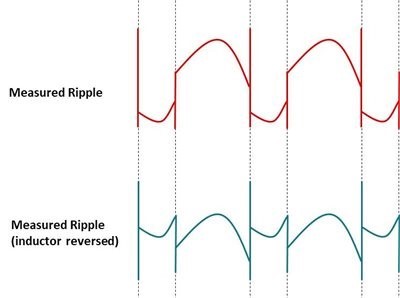

しかし、測定してみると、図2のようにエッジにスパイクがあり、(インダクタの向きを逆にすると極性が変わる)方形波成分が大きくなっています。

図2:測定した出力リップル

このような好ましくない成分はどこから来たのでしょうか。さらに重要なのは、これにどう対処すればいいかということです。

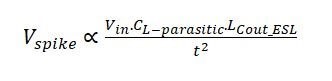

スパイク

インダクタを選択した際、自己共振周波数(SRF)はレギュレータのスイッチング周波数を上回��ており��すべて順調でした。もう一度見直してみましょう���インダクタには並列寄生容量があるため、SRFが存在します。スイッチング電圧の高速エッジが寄生容量に加わると、コンデンサを通って大きな電流スパイクが生じ、これにより出力コンデンサのESLに大きな電圧スパイクが生じます(式1を参照)。

(1)

このスパイクを抑えるには:

- より寄生容量が小さいインダクタを選択する。必要なインダクタンスと定格に対して最大のSRF値を探します。インダクタンスが低くなると、寄生容量も小さくなる傾向があります(同じく電流定格も低くなります)。そのため、インダクタンスまたは電流定格の仕様を大きくしすぎないようにしてください。

- 出力容量のESLを削減する。出力容量の要件に合う最小パッケージのコンデンサを選択します。複数の小型コンデンサを並列で使用することにより、各コンデンサのパッケージのサイズを(それによりESLも)小さくすることができます。また、インダクタを並列にすることでも、総ESLが削減されます。

- スイッチ・ノードの過渡電圧(dV/dt)を削減する(tの値を増やす)。スイッチ・ノードのエッジを直接制御できるレギュレータもありますが、それよりもブートストラップ・コンデンサと直列に小さな抵抗を配置して、エッジをスローダウンするケースの方が一般的です。これは効率に影響が出るかもしれないので、最初の2つの方法を選ぶ方がいいでしょう。

方形波

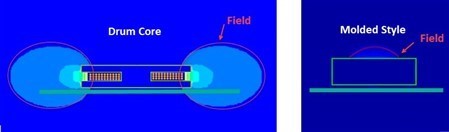

低コストの、シールドなしインダクタを選択したとしましょう。シールドなし(または樹脂シールド付き)のインダクタから出る磁場は、部品の実体の周囲にまで広がることがあります。図3に、シールドなしのオープン・ドラム型インダクタと、完全シールド付きモールド・インダクタの磁場をシミュレーションした図を示します。

図3:シールドなしドラム型インダクタとシールド付きモールド・インダクタの磁場(画像提供:Coilcraft)

このコンパクトなレイアウトでは、出力コンデンサがインダクタのすぐ右にあります。外に漏れ出た磁場は、コンデンサのESLと(いくらかは出力トラッキング・ループとも)結合し、方形波成分を生成します。インダクタの向きを逆にすると、インダクタの電流と磁場が逆になり(結合インダクタのドットが入れ替わるのと同じ)、そのため方形波成分も反転します。

この影響を減らすには:

シールド付きインダクタを選択し、このような結合の元になる漏れ磁束を抑える。シールドなしかセミ・シールドのインダクタを使用している場合は、平面寸法が大きく高さの低いインダクタを選択することで、エアギャップの高さが低減してフリンジング磁束も減少します。

前述の方法で出力容量のESLを削減する。

磁場が最も大きくなるインダクタのすぐ近くに、出力コンデンサとトラッキングを配置しない。スペースの制約が厳しい場合は、クラムシェル構造にして、他のレギュレータ回路に対して基板の逆側にインダクタを配置できないか検討してください。これにより、磁場が最も強いインダクタのプレーンから出力コンデンサを離すことができます。

これで、出力リップル波形を確認して、いろいろな部品を取り出せるようになりました。外付けのパッシブ部品を適切に選択し、注意してレイアウトを決めることによっても、小型で費用対効果の高いソリューションの実現と、アプリケーションの出力リップルの最適化が可能になります。

参考情報

+「Analog Design Journal」の記事(英語):“Select inductors for buck converters to get optimum efficiency and reliability”

+ アプリケーション・レポートのダウンロード:“Output Ripple Voltage for Buck Switching Regulator”および“Space Optimized, ‘Clam-Shell’ Layout for Step-Down DC/DC Converters”

※すべての登録商標および商標はそれぞれの所有者に帰属します。

※上記の記事はこちらの技術記事(2020年6月18日)より翻訳転載されました。

※ご質問はE2E Support Forumにお願い致します。