Other Parts Discussed in Thread: , AM62D-Q1, , SYSCONFIG

Hi TI Experts,

Can you provide a List of collaterals that can be referred when starting a custom board hardware design.

Hi Board designers,

The below links are a quick reference to the collaterals that can be referred when starting a custom design.

Device Selection and features

Product Pages

https://www.ti.com/product/AM62P

https://www.ti.com/product/AM62P-Q1

Datasheet

AM62Px Sitara Processors datasheet

https://www.ti.com/lit/pdf/sprsp89

Silicon Errata

AM62Px Sitara Processors Silicon Errata, Silicon Revision 1.0, 1.1

https://www.ti.com/lit/pdf/sprz574

Technical Reference Manual

AM62Px Sitara Processors Technical Reference Manual

https://www.ti.com/lit/pdf/spruj83

Custom Board design:

Hardware Design Considerations

Hardware Design Considerations for Custom Board Using AM62P / AM62P-Q1 Family of Processors

https://www.ti.com/lit/pdf/sprada9

Schematic Design and Review Checklist

AM62Px Processor Family specific checklist (Recommended)

AM62P, AM62P-Q1 Processor Family Schematic Design Guidelines and Schematic Review Checklist

https://www.ti.com/lit/pdf/spradn4

AM62X processor families (For references)

AM62x, AM62Ax, AM62D-Q1 and AM62Px Processor Families Schematic, Design Guidelines and Review Checklist

https://www.ti.com/lit/pdf/sprad21

Power Consumption

AM62P Power Estimation Tool

https://www.ti.com/lit/pdf/sprujd9

Evaluation - EVM

SK-AM62P-LP Design Package Folder and Files List (Rev. A)

www.ti.com/.../SK-AM62P-LP

www.ti.com/.../sprt780

SK-AM62P-LP Design File Package

https://www.ti.com/lit/zip/sprr487

Schematics (Reference) for RMII interface

Note: We did functionally validate the common clock configuration. No other clocking options were tested.

Ethernet PHY daughter card

https://www.ti.com/tool/DP83867-EVM-AM

https://www.ti.com/tool/DP83826-EVM-AM2

https://www.ti.com/tool/TIDA-00928

There seems to be a muxed GPMC interface implemented.

https://media.digikey.com/pdf/Data%20Sheets/Texas%20Instruments%20PDFs/TMDXICE3359_SCH.pdf

CAD symbols

CAD symbol specific to the selected device can be chosen from the device product page. Refer below example

https://www.ti.com/product/AM62P#cad-cae-symbols

Ordering & quality

https://www.ti.com/product/AM62P#order-quality

https://www.ti.com/product/AM62P-Q1#order-quality

Package pad diameter and substrate pad dimension

AM62P / AM62P-Q1 -> AMH pkg : ball diameter 0.4mm : substrate pad 0.35mm

The recommendation is 1:1 ratio between PCB pad and substrate pad.

DDR Board Design and Layout Guidelines

AM62Ax, AM62Px, AM62Dx LPDDR4 Board Design and Layout Guidelines

https://www.ti.com/lit/pdf/sprad66

Escape Routing for PCB Design

AM62Px Escape Routing for PCB Design

https://www.ti.com/lit/pdf/sprad96

Design Simulation files

https://www.ti.com/product/AM62P#design-tools-simulation

Simulation files provided includes IBIS, IBIS-AMI, BSDL and Thermal model

AM62Px PDN Target impedance Values:

| Voltage Rail | Freq Range | Target Impedance (mOhms) |

| VDD_CORE (0.75V) | Low (< 1MHz) | 14.25 |

| Mid (1 - 20 MHz) | 23.75 | |

| High (20 - 50 MHz) | 47.5 | |

| VDD_CORE (0.85V) | Low (< 1MHz) | 12.1125 |

| Mid (1 - 20 MHz) | 20.1875 | |

| High (20 - 50 MHz) | 40.3750 | |

| VDDS_DDR (1.1V) | Low (< 1MHz) | 9.8 |

| Mid (1 - 20 MHz) | 13.0 | |

| High (20 - 50 MHz) | 34.0 |

For frequencies above 50 MHz the board decoupling caps do not play a critical role. SoC and Package decaps (if any) will be dominant beyond 50 MHz

Note: We do not include Buck output inductance in PDN simulations.

For VDDS_DDR: we do not recommend using target impedance as the signoff for DDR.

Refer to the AM62Ax, AM62Px, AM62Dx LPDDR4 Board Design and Layout Guidelines which outlines all details of power aware SI/PI simulations

that need to be run. The eye mask checks from these power aware simulations are the signoff.

We only provide impedance targets for VDD_CORE. This information can be found under processor specific section "Example:AM62Ax" (starting on page 31) in the following document: www.ti.com/.../sprac76

As noted in the document, rails not listed are not simulated by TI due to low load transients. For more information, see the device-specific EVM layout for example implementation of these rails.

Other rails like the IOs are highly dependent on external peripherals. From the SoC perspective, if you look at the MAX current ratings for the IOs, the total current (after combining all the IOs of the same voltage) is still very low < 350mA so we don't simulate this rails/No data available.

Regarding your other questions related to PET, the supply names are not expected to match with processor (Example AM62A) pin names because the power estimates in the PET are itemized by supply groups. The power supply consolidation for these supply groups match the EVM.

Power Distribution Networks: Implementation and Analysis

Sitara Processor Power Distribution Networks: Implementation and Analysis

https://www.ti.com/lit/pdf/sprac76

High Speed Board design and Signal integrity simulation

https://www.ti.com/lit/pdf/spraar7

https://www.ti.com/lit/pdf/spracn9

SYSCONFIG

DDR subsystem register configuration tool

Technical Documents

Collaterals and application notes

https://www.ti.com/product/AM62P#tech-docs

https://www.ti.com/product/AM62P-Q1#tech-docs

Technical Support

AM62P / AM62P-Q1 Custom board design - FAQs

Previous E2E threads - Keywords AM62Px, AM62P, AM62P-Q1

Starting a new thread

Useful links

Sitara family of processors FAQ master list

Other FAQs

Notes

Regards,

Lavanya M R.

Hi Board designers,

Inputs regarding Package shelf life

Please refer below links

https://www.ti.com/support-quality/quality-policies-procedures/product-shelf-life.html

https://www.ti.com/support-quality/faqs/product-shelf-life-faqs.html

https://www.ti.com/support-quality/reliability/reliability-home.html

https://www.ti.com/lit/an/spraby1a/spraby1a.pdf

https://www.ti.com/lit/pdf/snoa550

https://www.ti.com/lit/an/slva840/slva840.pdf

/cfs-file/__key/communityserver-discussions-components-files/791/Baking-Procedure.pdf

I got the ask from a customer if we define the storage air humidity and the air humidity in operation for the AM62P?

I guess not, but I wanted to doublechekc with you.

Also, this is the requirements they are asking for:

Prior to board assembly but removed from sealed packaging -> device is specified as MSL3, rated for 168hrs exposure at ≤30°C/60%RH ambient conditions without a re-bake being required before board assembly.

We have no spec for operational humidity specification, but device completed and passed relevant qualification at MSL3 moisture precondition + 1000hrs 85°C/85%RH THB (Temperature, Humidity, Bias) per standard JEDEC test conditions

Regards,

Sreenivasa

Hi Board designers,

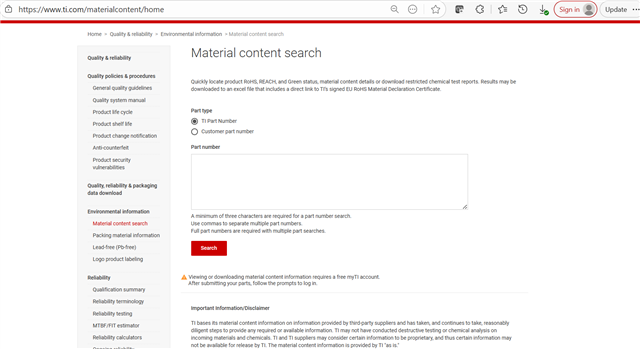

Inputs regarding weight and material content

https://www.ti.com/materialcontent/home

Regards,

Sreenivasa

Hl Board Designers,

Please refer below inputs related to powering E2 SK.

FYI, The USB power detection logic has been updated in the E2 version

AM62P-Q1: New EVM procured (SK-AM62P-LP) board not powering up.

I can see the E2E thread in that I have seen below, let me clarify the situation, the customer is using two E1-1 board is working and one E2 board is not working. The E2 board has a additional logic for VMAIN load switch see below . This load switch enable controlled by PD controller. When ever the PD not seeing 15W negotiation then it won’t enable the load switch. So here on E2 board I can see TP82 (VMAIN) is 0v and C112 & C123 (VMAIN_PD) is 5.27V that means the below load switch is not enabled due to PD power negotiation issue or some other soldering issue. So I recommend first to check with recommended power supply then replace the board.

Can you please confirm the below to proceed with return authorization:

If they’re using it with Type-C to Type-C cable and it’s the only device plugged into the adapter (so it’s not falling back to power sharing modes) then it looks like it should work fine, they might have a board issue after all.

I tried with a 25W charger C-C type, it worked

Regards,

Sreenivasa