Hi Team

For DAC output "buffer + differential to single ended" scheme, please help confirm whether THS3215 HD2 (40MHz 1vpp) supports < - 75dbc, or there are other schemes。

Thanks in advance

Best regards,

William

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi William,

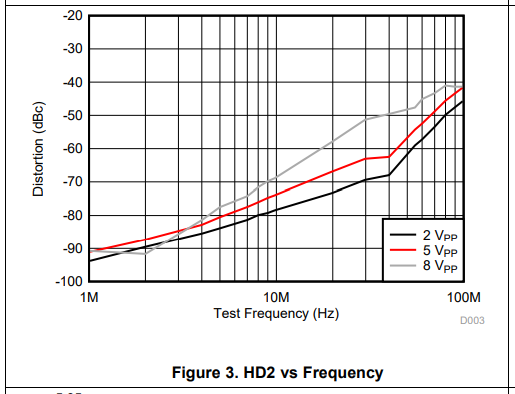

The data we have available for differential to single ended HD2 over frequency is at specified at 2Vpp:

It looks like 1Vpp at 40MHz probably puts you around -70dBc. Could you clarify what you mean by other schemes?

Best,

Sam

Hi Sam

Thanks for your kindly reply,

Is there a way to improve HD2 performance to -75dBc

Thank you a lot.

Best Regards,

William

I believe the plot Sam put in was for the combined D2S +OPS into 100ohm load. That plot shows about -69dBc for 2Vpp, it should get a little lower for a 1Vpp swing and if you were to increase the loading on each stage a little.

-75dBc is a pretty good number at 40MHz, keep in mind these are typical plots and you should anticipate some spread around this (most likely in the worse direction).

Hi Team

Thank you for your letter. We haven't found a solution yet,

Is there a chance to increase the voltage (+ / - 6V - > + / - 7.5V) to get better HD2? How much can it increase?

Or other models of buffer + differential to single end DAC output amplifier are available

Best Regards,

William