Other Parts Discussed in Thread: TINA-TI, , INA181, INA303, INA302, INA301, INA300, INA381

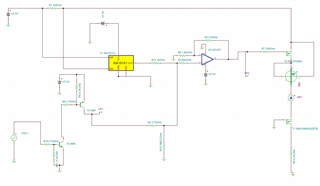

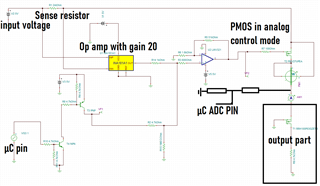

2068.output current protection control at 2A75.TSC

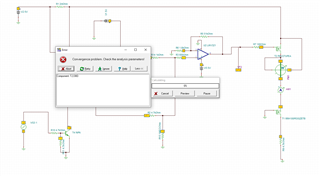

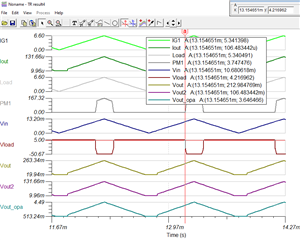

I developed some circuitrary but I am getting error of convergence problem. I checked all circuit parameter but still the error present. Can you please tell me what exactly this error message means ? and how to resolve such issues?