Other Parts Discussed in Thread: OPA2388, OPA388, OPA348

Hello,

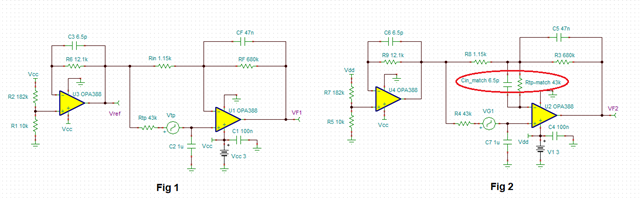

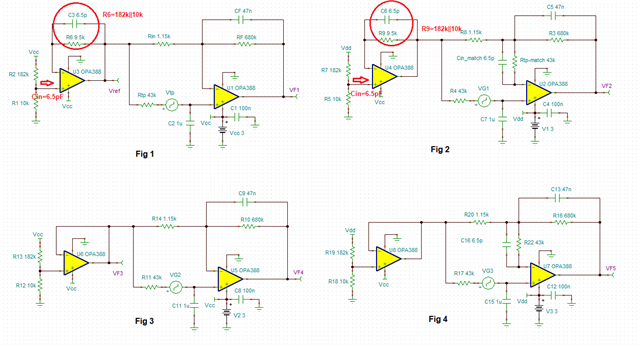

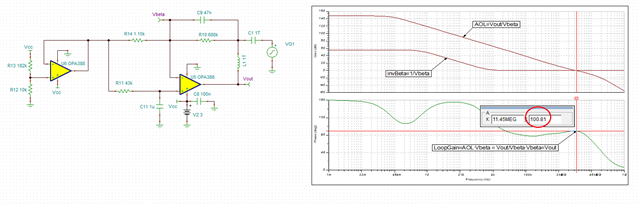

I have been suggested to use a configuration which matches the impedances at the + and - inputs, in the related previous post.

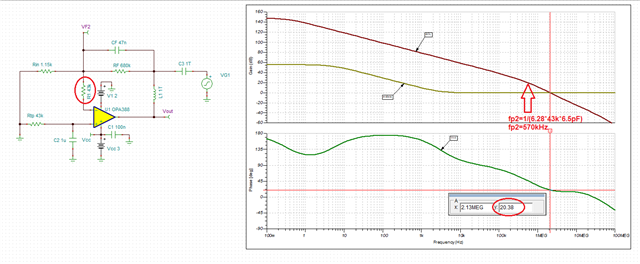

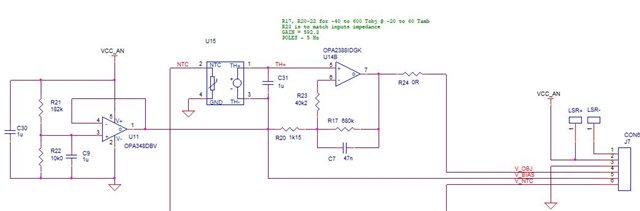

I dunno if there's something 'hidden', something I've not yet understood but using at the - input a resistor with the nearly same value the one at the + input gives a very big offset output: in the circuit below the output was nearly 0 V, having a common input of 156 mV. The sensor U15 is a thermopile, whose resistance is 43 kOhm.

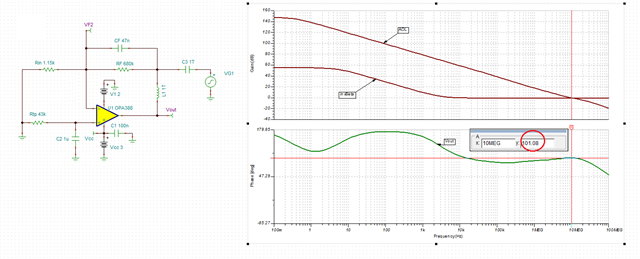

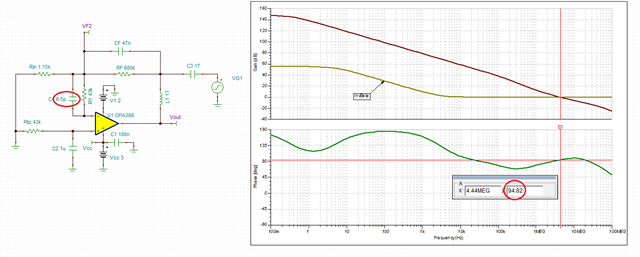

Removing R23, gives an offset values RTO of few mV but the big troubles is that it is not stable.

at power on it is around -2.4 mV, after 15 minutes is around -11 mV and then it moves slowly between -11 and -9.5 mV.

If I use a fixed 43 kOhm resistor in the place of U15, the offset appears nearly neglectable (less the 0.25 mV) and stable (still without R23; with R23 the offset is very high again).

I could image that the sensor U15 gets some noise, EMI and hum and they can become relevant because the gain is high, currently ~592. Or it is something related to the COMMON MODE which the internal switching "transforms" into undesirable offset.

What I ask you is a help about those offset variations: having offset is OK, it can be compensated in the subsequent processes but what I cannot compensate is its variation!

Due the very low output of the sensor, I have chosen an OPAMP with nearly no-drift in the offset with temperature..... Currently I have the OPA4388 in the prototype board, later I'll use OPA2388 or 2387...

Any suggestion ?

Thanks

Maurizio