Other Parts Discussed in Thread: OPA695, LMH6702, THS3217, THS3215, OPA684, THS3092, OPA4872

Dear all,

I guess it is a simple question but due to my lack of experience in analog electronics I would like to be sure of what I do.

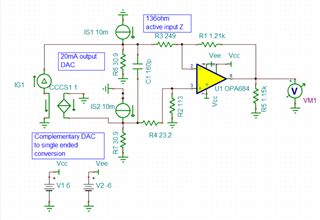

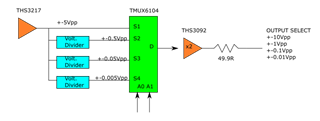

I am using AD9707 DAC from Analog Devices. I want to single-ended buffer the output as in pag. 40/42 of the datasheet but using THS3001 instead of ADA4899. I have configured the DAC so IFS=2mA (RSET=16K)

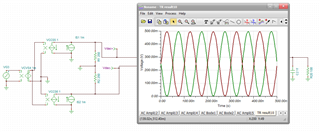

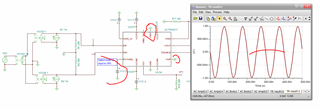

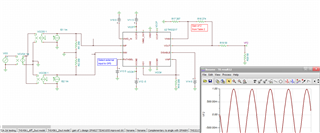

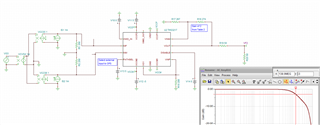

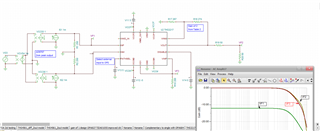

I want VOUT (after the THS3001) to be 2Vpp (-1V/+1V). I trying to use similar schematic as in DAC datasheet and I have simulated with TINA but without success. Please find attached an image of the simulation.

DAC is simulated as a current source 0-2mA. For Rs I am using 49,9Ohms. REFIO is 1V (Internal of DAC)

How should be the schematic for the output I need? Is the DAC well simulated with a current source of 0-2mA? If not, how should I simulate it? is RS correct or what other value should I use?

Thanks in advance.

Joaquin

.