Other Parts Discussed in Thread: REF3333,

Dear TI E2E-Team,

thank you for this greatly managed forum and your support.

Currently we have a problem with the current sensing circuit of a PMSM motor drive board.

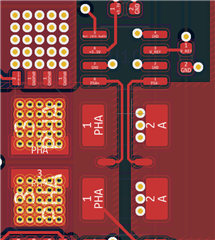

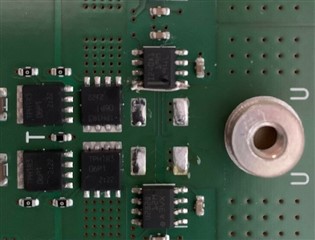

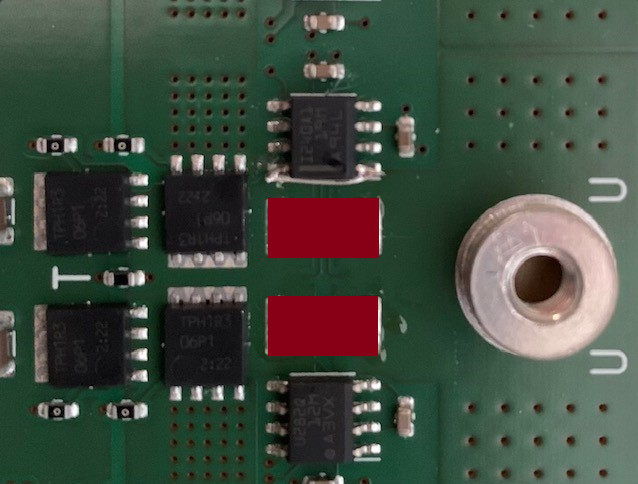

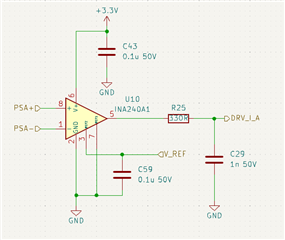

We are using three INA240A1 for sensing the phase currents inline:

The PSA+ and PSA- are Kevlin connected to the shunt resistors and the DRV_I_A signal is connected to an ADC input. The V_REF input is taken directly from a REF3333 voltage reference.

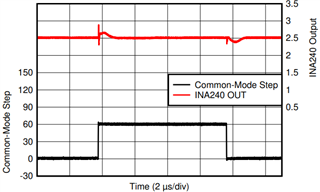

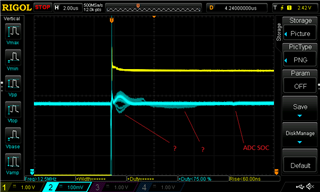

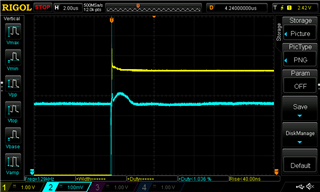

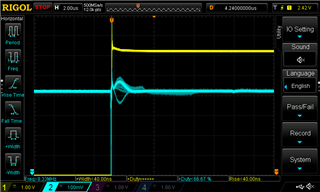

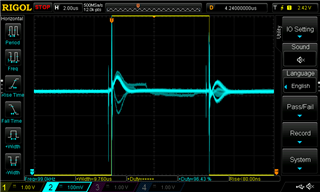

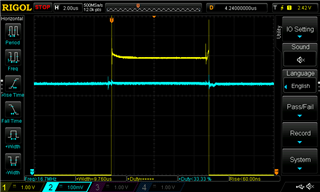

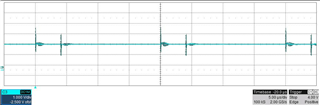

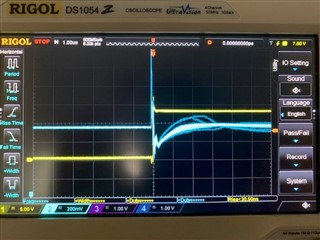

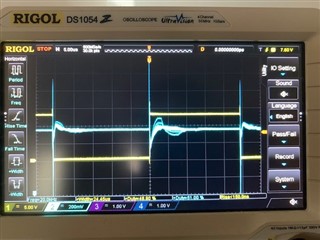

When driving the motor phases with 50% duty cycle and no load, we see the INA240 output behaving unexpectedly: Sometimes there are completly different signal waveforms:

Channel 1, yellow: PSA- / Phase Output

Channel 2, blue: DRV_I_A / INA240 Output

The long settling time and strange waveforms make our ADC readings not usable. What are we experiencing here?

Thank you for your support.

Ben