Other Parts Discussed in Thread: ADS1675, THS4130, TINA-TI, THS4551, THS4541

This probably applies to all the THS diff amp products.

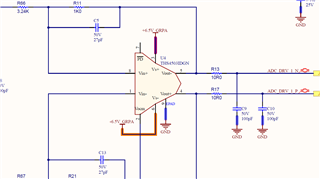

I am using the amp as an ADC input with VCOM offset as well. I have a gain less than unity and I have heard that it can be unstabl;e with less than unity gain. I simulated it in spice and it was stable.Below is the circuit,

I did add the two feedback caps to flatten the bode plot at the knee, but otherwise it was stable. I am driving an ADS1675