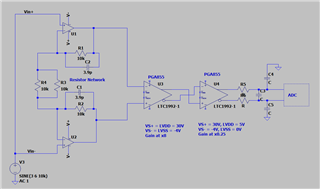

Other Parts Discussed in Thread: OPA2140, INA851, OPA2828, PGA855, OPA140

Tool/software:

The previous thread was locked.

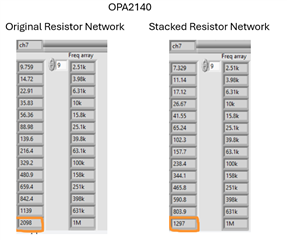

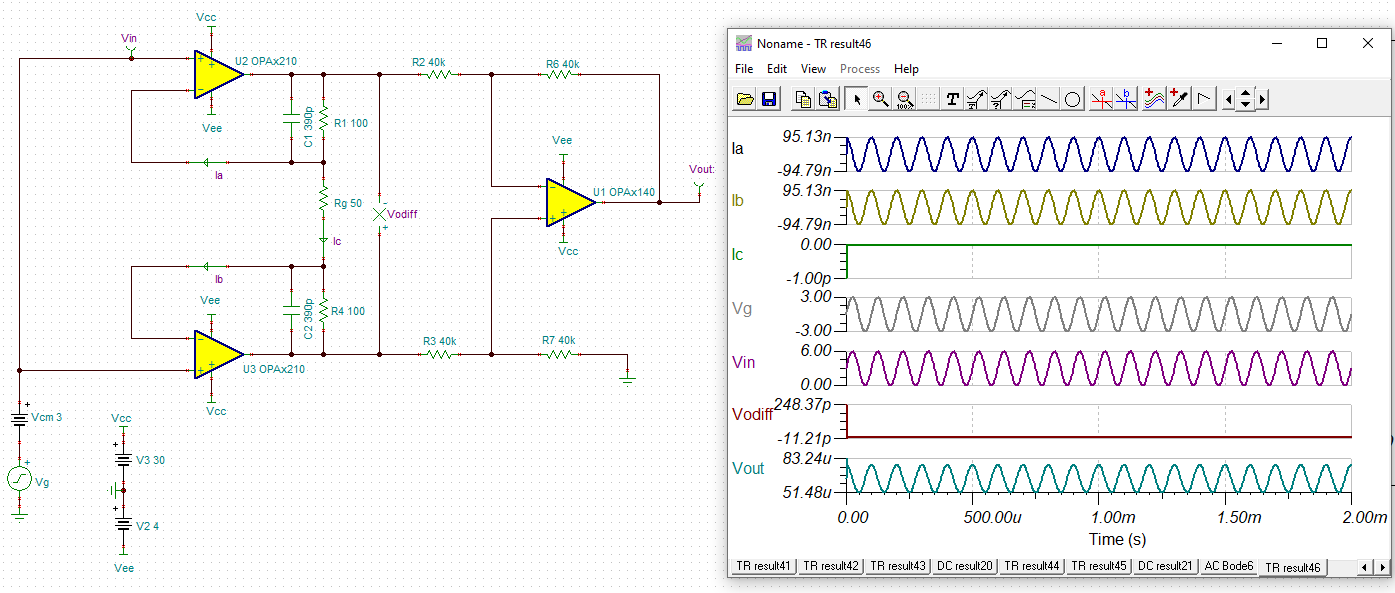

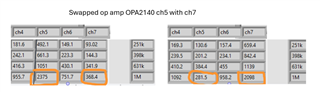

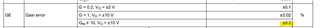

I stacked another resistor network on OPA2140 feedback, and the CMRR improved. The unit is in uV/V

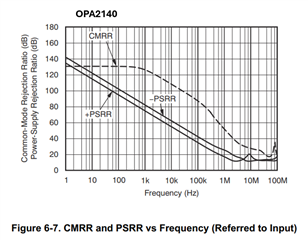

While this experiment shows the feedback network does affect the CMRR, the result is still off from the datasheet figure of ~32uV/V (-90dB) at 100kHz

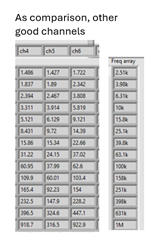

Also, not every channel is this bad: These channels are with original resistor network values.

These channels are with original resistor network values.

So I feel like this could be a device to device variation, just that it has quite a big spread.

Appreciate if the team can provide more insights.

),

),