- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

Tool/software:

Title: Op-Amp Behavior Differences After Repeated Use: Could It Be Soldering or PCB Material Issues?

Hello Team,

I am facing an issue with two identical buffer circuit boards, and I’m trying to understand why their performance differs. I suspect it might be related to either the handling/soldering process or PCB material. Here are the details:

Setup:

Observations:

Questions:

Below are the test results from both boards 2nd board result:

2nd board result:

First board result

Could this behavior be due to handling or soldering issues?if soldering might be the issue can you please tell me what precautions to take care(Temperature etc). For example, is the op-amp being damaged during assembly or subsequent handling? while handling i am making sure of ESD protection.

so can you please help me where it is going wrong in simple buffer mode?

Hello Deepthi,

Thank you for the details on the issue. The board material here shouldn't be the issue. I have a few more questions:

Thank you,

Sima

thanks for the reply team,

1.Sorry for the confusion earlier. The results I provided were obtained with decoupling capacitors soldered at the supply. In this setup, only the decoupling capacitors at the supply, one terminal block to provide input from the supply, and the op-amp are present on the board. No other components are soldered.

2.Yes, on one board when the quiescent current increases significantly, desoldering and soldering a new op-amp brings the quiescent current back to the values mentioned in the datasheet. During this time, I noted the buffer characteristics, but the bias currents and offset voltages were not correct. However, after the 2nd or 3rd run, the quiescent current starts to increase again.

same on one board where everything is working fine as per the datasheet specifications, I’ve replaced the op-amp only twice, and the results have been consistent both before and after the replacements, remaining within the datasheet specifications.

Hello Deepthi,

Thanks for the information! Sorry I didn't include this in first reply, I just noticed that you are testing up to 5V at the input, is this correct? If that is the case, the max voltage range for a device set to voltage supply configuration of +/-2.5V is -2.5V to 1.1V at the input (abs max is +/-0.5V from the supply). Would you be able to rerun the tests between these values, and update us if it still is damaged after each 2nd or 3rd run?

Thank you!

Sima

okay , but when i am going for 10meg and 1meg ohm resistance as Rf and Rg why my output is getting stucked at 2.09V. why its not increasing or decreasing even though i am changing the input voltage , i operated at +5 and 0V supply with Vcm =3.4V , will this op amp is not suitable for Mega ohm resistors as feedback . can you please tell me why i am not getting results as expected with this resistor configurations.

Hello Deepthi,

The OPA858 does have very low input bias due to its input CMOS structure, but we still would discourage using very high resistance values when not necessary due to stability. Does this only occur when using high resistor values?

Thank you,

Sima

Thank you so much for the reply ,

I want to use the OPA858 in a trans impedance amplifier (TIA) configuration with a 1 GΩ feedback resistor . However, I noticed that stability issues arise when Rf > 100 kΩ. Will the OPA858 be suitable for this high-gain application? If so, how can I ensure stable operation and determine the correct operating points? this opamp i choosed because lt spice simulations are matching with my constraints. can you please help me with this team .

Hello Deepthi,

1GOhm feedback resistor might be too high, but OPA858 should work within the MOhm range in a TIA configuration. The stability could be because of your input vs feedback capacitor. What is your input and feedback capacitance? Or are you testing with no diode (input capacitance)?

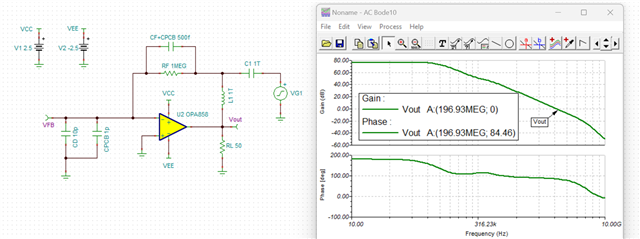

To determine stability via simulation, I have two examples below: (anything above 45 degrees phase margin at 0dB crossing is considered stable)

First Version:

Second Version:

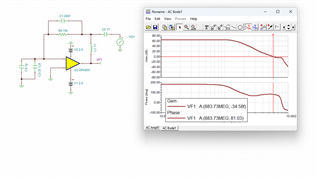

I tried it with OPA858, with 1MOhm resistor with below configuration:

Thank you,

Sima

Madam thabks for the reply , can you please clarify this doubts.

For now, I am testing without any input capacitance and feedback capacitance, as I am only checking DC currents. I am not using a diode as the input source; instead, the input will come from another device. However, PCB parasitic capacitance will still be present. For my actual application, I need to work within a 10 kHz bandwidth, so I will include the appropriate feedback capacitor in the simulation accordingly. Since I am not using a diode, I am ignoring C_diode in my analysis.

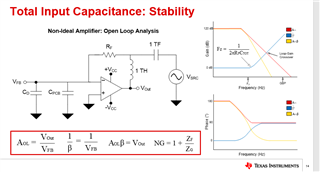

Regarding your stability analysis setup, what I know is that to check stability, we usually break the loop at the inverting terminal and apply a voltage source between the inverting terminal and the feedback network while grounding the inputs. But in your case, I am not sure what V_fb represents and what should be applied toVfb and V_g1. Also, the gain plots you shared—are they showing V_out/V_g1, or something else?what is Vfb is it grounded ? Could you clarify this?

Additionally, I noticed extremely high component values like 1 Tera-Farad (1 TF) and 1 Tera-Henry (1 TH) in your setup. Are these just theoretical components for analysis, or are you considering them for real implementation? In practical circuits, such extreme values are not feasible.

and is the phase margin in the last case with opa858 is it 180-84.46 =96.54 or just 84.46

Hello Deepthi,

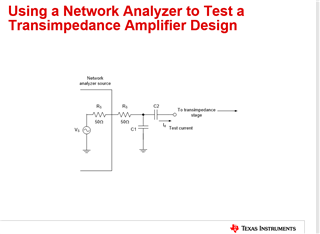

I apologize for delay in response. For the best method to test out TIA based device without a photodiode, I would suggest using a voltage source and add a couple passives at the input to the inverting pin of the amplifier with estimated input capacitance and feedback capacitance. Otherwise, the entire system might not be stable due to these missing components that add the pole/zero pair to move move the AOL + noise gain crossover to above the second pole of the AOL especially with a decompensated amplifier. The attached PowerPoint below shows how to do use this method (slide 41 and 42)

With 10kHz bandwidth, this will be easier to achieve by increasing the feedback capacitance slightly, but making sure 1 + (Ctot/CF) is greater than 7V/V for device stability.

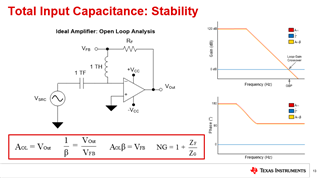

For stability question, you are correct in breaking the loop. The VFB and Vout refer to nodes where they are used to find AOL, noise gain, and loop gain. Where AOL and noise gain crosses is where loop gain = 0dB which is where phase margin of the system is determined. The equations based on where you break the loop (either at the input or output), are below:

We have a stability analysis video that is very helpful for more detailed information: https://www.ti.com/video/4080235259001. Please click on Precision lab video series for the rest of the stability series on section 10.

For the extremely high component values like 1 Tera-Farad (1 TF) and 1 Tera-Henry (1 TH) in the setup. You are correct these values are not feasible and are just theoretical components for analysis to open the loop at AC, but have a DC path for simulation to converge. You would not do this in a practical real life sense.

And, the last question on if the phase margin in the last case with opa858 is it 180-84.46 =96.54 or just 84.46, it is just 84.46. This is because it is 84.46 away a complete 180 degree phase inversion which would cause complete instability (45 degrees away from 0 is the safe zone, and 90 degrees shift from 180 is standard due to AOL's first pole (180-90), anything between 90 and 0 would be where your phase margin would land). You are on the right track to mention subtraction from 180, this is if the simulation starts at a value different from 180, that way you should subtract from your starting point to 180 phase inversion to be able to calculate phase margin, but in this case simulation starts at 180, so no need to do subtraction.

3201.Transimpedance design flow using high speed op amps.pptx

Thank you,

Sima

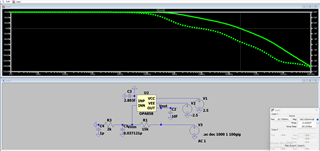

I designed an inverting amplifier with a gain of 7.5 V/V and included PCB parasitic capacitances at the inverting input, non-inverting input, and output, voltage capacitance After performing a loop gain stability analysis by breaking the loop at the output, I observed a phase margin of 14°.

Is my circuit unstable even in the simple inverting configuration? How can I improve stability while maintaining the same gain? Attached is my simulation file for reference.

Thanks!

Hello Deepthi,

Thanks for the update. For a true TIA application, please remove R3, and add a feedback capacitance for stability. The feedback cap and input cap is what create the pole/zero pair for proper stability.

You can see the phase go down then up again, this is the pole/zero pair placement to increase phase before 0dB crossover in order to have a stable system.

Best Regards,

Sima

Op-Amp Circuit: DC Offset at Output Causing Saturation Issue

Hi everyone,

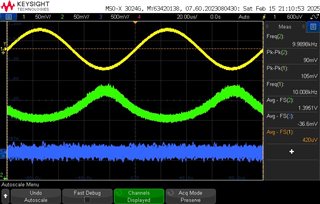

after doing all this stabiiity analysis in opamp also ,I'm facing an issue with my op-amp circuit where a DC offset at the output is limiting the available swing and causing saturation when I increase the input amplitude.

I am getting an amplified sine wave at the output with the same frequency as the input, but the DC offset at the output is limiting the swing. When I try to increase the input amplitude of sine wave , the output saturates instead of providing the expected gain. so why am i getting dc offset at input , which is eventually amplifying and giving dc offset at output , which saturates the sine curve in oscilloscope .

at inverting terminal of the opamp there is some dc which is coming from somewhere ,not from the function generator which is causing my output to go into saturation.

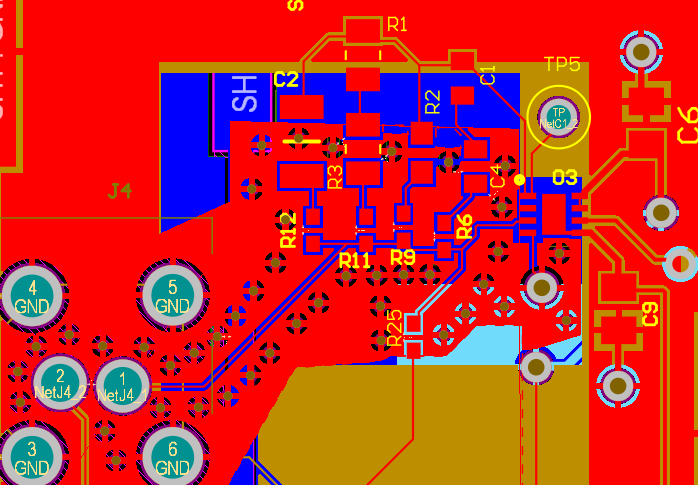

so yellow color graph is input which i gave from function generator , green color graph is the output of teh opamp where the sc is 1.36 .. and please ignore blue color graph , and the circuit layout diagram is attached

so yellow color graph is input which i gave from function generator , green color graph is the output of teh opamp where the sc is 1.36 .. and please ignore blue color graph , and the circuit layout diagram is attached

can you please help me with this.