Other Parts Discussed in Thread: OPA192

Hi Team,

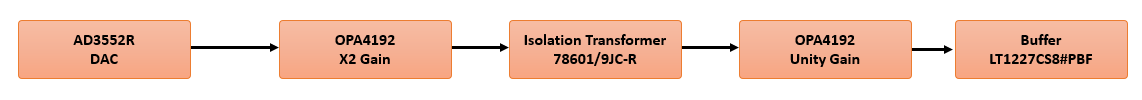

I'm using the amplifier OPA4192IPWR in my board. I'm providing the output of the DAC AD3552R to the OPA4192 amplifier in my design and also used as a unity gain amplifier in another case.

The signal chain diagram is shared below

1. As it is a channel amplifier, i want only the 3 channels for my application. Can i make the unused channel as NC or any specific termination is required.

2.Is Riso resistor and Cload is mandatory in the circuit. If mandatory which values should I choose.

3.For unity gain amplifier does the below circuit is correct. Please confirm whether Riso and Cload values are okay.

Regards,

Abhishek