Other Parts Discussed in Thread: INA240, INA282

Hi team,

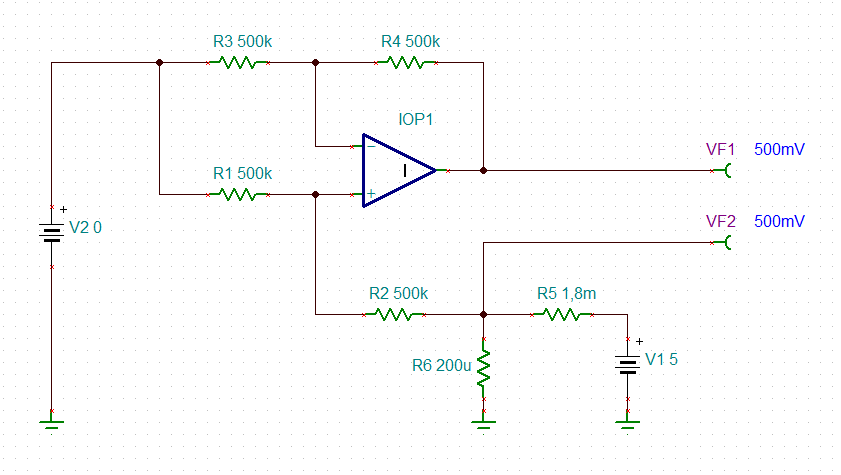

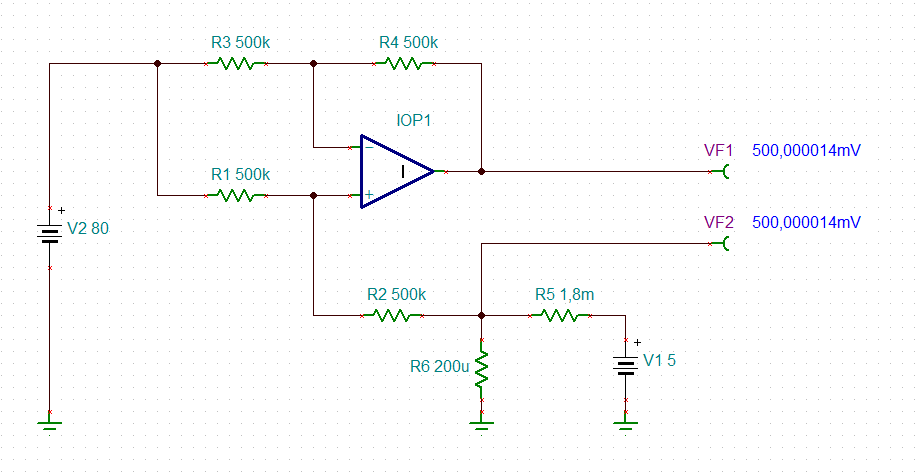

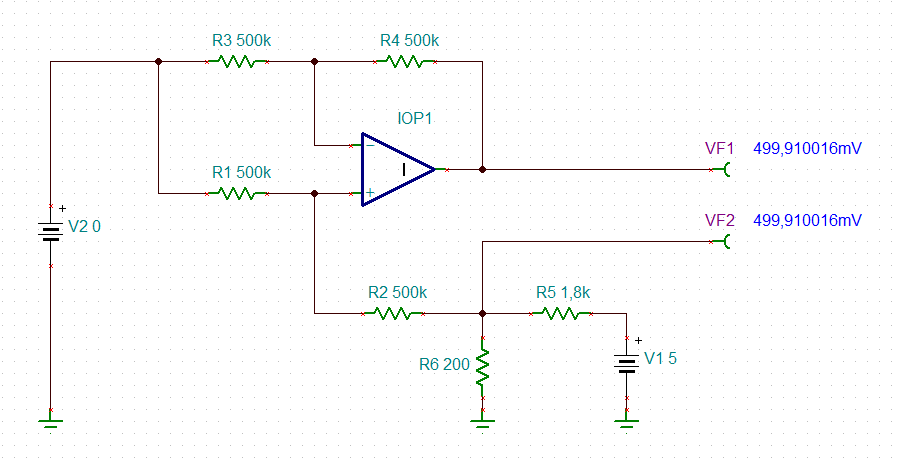

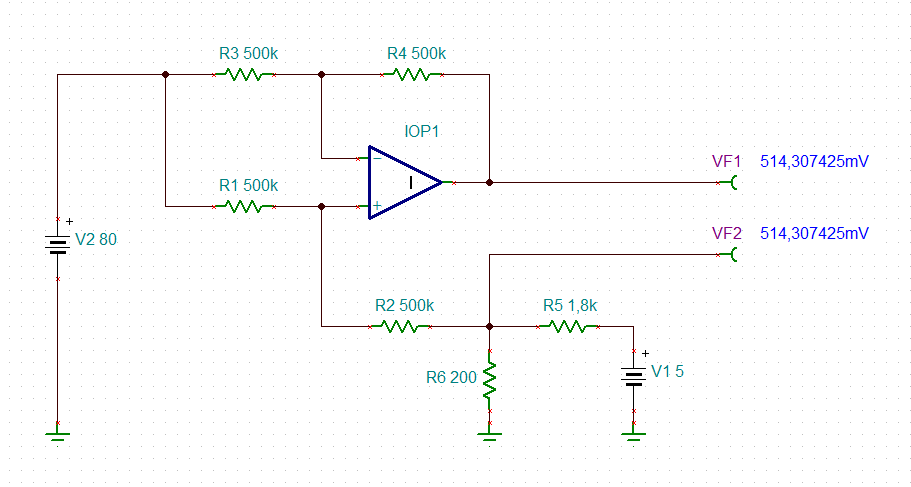

We are considering using INA240 as shown in the following figure.

Could you tell me the resistance value in red?

In our usage, current flows in from IN +, and the REF2 and REF1 voltages rise above the set value.

It is necessary to know how much the resistance value of R1 and R2 should be set.

Best regards,

Tomoaki Yoshida