Hi Team,

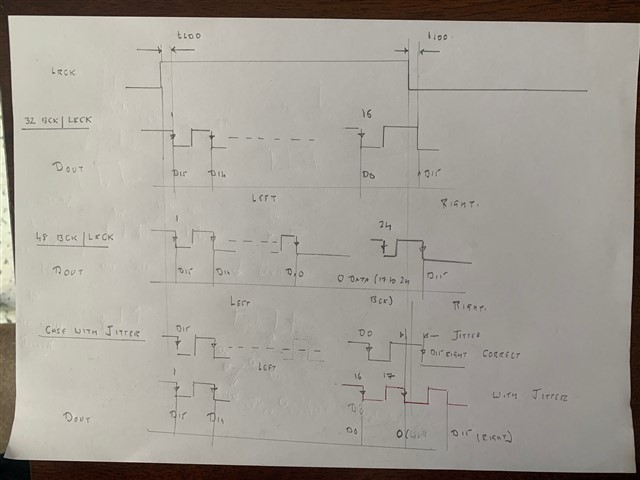

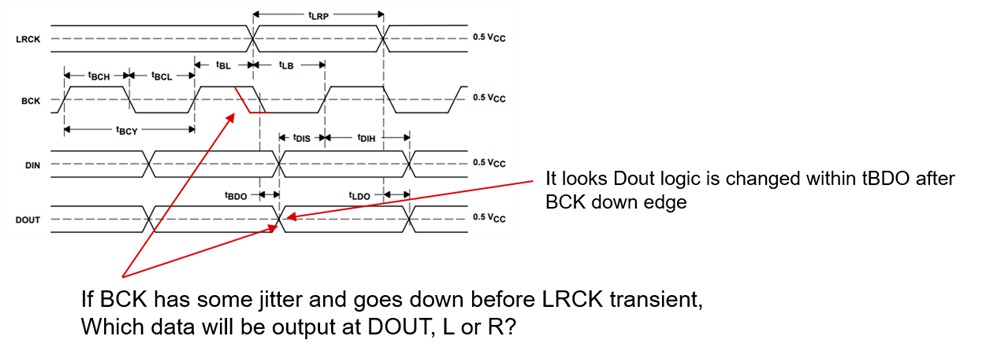

Could you tell me which clock Do output timing is based on, LRCK or BCK?

BCK clock has some jitter in my customer system and sometimes it goes down before LRCK down edge. They chose left-justified mode so they would like to confirm how dealing with the first bit data if BCK goes down before LRCK down edge.

Regards,

Takashi Onawa