There is a internal clock error happened during the sound generation process.

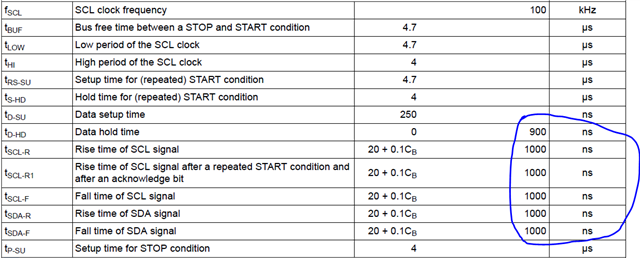

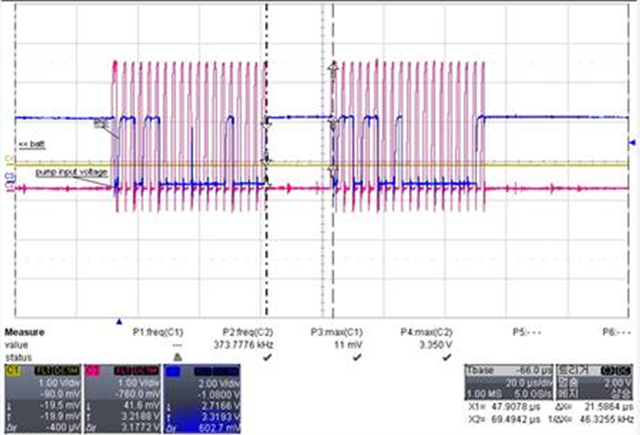

When the issue happened, we tested the I2S clock as below(12K sampling rate is used).:

|

Test results(Ratio/fs) |

LRCK |

MCLK |

SCLK |

fs |

Result |

|

Normal sample without CLKE |

12.04399 |

6163.678 |

771.231 |

12 |

|

|

Ratio with Fs |

1.003666 |

513.6398333 |

64.26925 |

|

PASS |

|

Design Ratio(xfs) |

1 |

512 |

64 |

|

|

|

Error clock critia -10% |

10.8 |

460.8 |

57.6 |

|

|

|

Error clock critia +10% |

13.2 |

563.2 |

70.4 |

|

|

|

|

|

|

|

|

|

|

Abnormal sample with CLKE |

12.0439 |

6156.04 |

770.9 |

|

|

|

Ratio with Fs |

1.003658 |

513.0033333 |

64.24167 |

|

PASS |

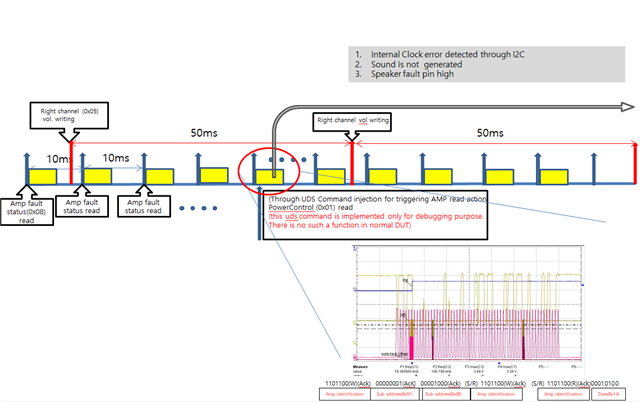

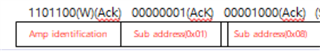

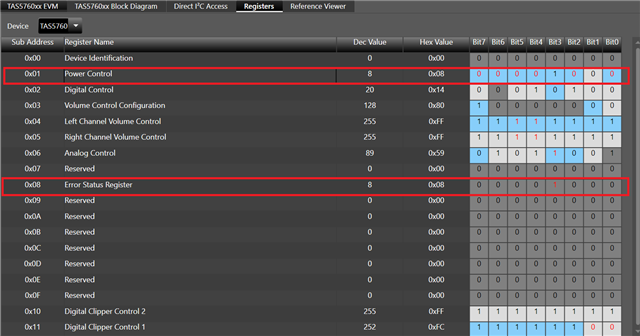

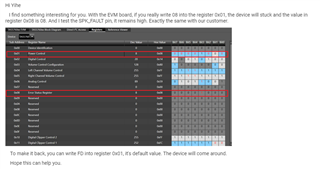

Based on datasheet, the AMP should be recovered, however, the AMP seemed to be stuck after internal clock error happened.

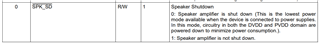

May we know what kind of conditions can trigger AMP stuck in the clock error status. When the clock issue happened, the SPK_SD and SPK_FAULT is high which meant AMP is no issues.

The I2S sound data from MCU is also normal, however, the AMP output is no sound.