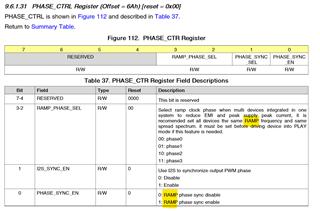

The datasheet lists on page 64 that it is possible to sync the output PWM via I2S. So for example if I use 5 TAS5806MD devices and configure those registers so that all 5 devices are synced to the I2S which output PWM frequency will then those devices have? Is it n-times the LRCLK or n-times the BCLK? and how large is n?

Also on the same page: what do you mean with RAMP clock phase or RAMP frequency? I must have missed the meaning of RAMP. Therefore what does RAMP phase sync do exactly?

I am asking because I would like to sync a lot of TAS5806MD devices together and by chance also sync it with a buck regulator.