We have a design in which we are sending 16-bit samples at 8 kHz sample rate to be played on a Class-D speaker. The audio quality is fairly bad. Even sending a 440 Hz sine tone on the I2S bus results in a distorted sounding tone. The peaks at the 440 Hz harmonics are actually higher than the peak at 440 Hz, itself. Also, there is a peak around 8000 - 440 (7560) Hz indicating aliasing.

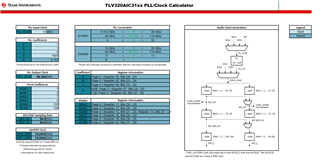

I am interested in any suggestions, but I suspect at least part of the issue is my DAC clocking configuration, and I wanted some clarifications. We do not provide MCLK and are using BCLK (2 * 16 * 8 kHz = 256 kHz) as PLL_CLKIN. We then set the PLL values as follows: P=1, R=1, J=32, D=0. So PLL_CLKOUT is 32 * 256 kHz = 8.192 MHz. We then use NDAC=4, so DAC_CLK is 2.048 MHz, and MDAC=4, so DAC_MOD_CLK is 512 kHz, and DOSR=128, so DAC_fS is 4 kHz.

Some of my questions are:

- Should DAC_fS always match the I2S WCLK?

- Is there a suggested DOSR value for 8 kHz sample rate?

- How is DAC_CLK used on the TLV320AIC3110 since it doesn't have a miniDSP?

- Is there any required relation between NDAC and MDAC?

Also, I see that the PLL input supports clocks varying from 512 kHz to 20 MHz, so our BCLK of 256 kHz is out of spec. I suppose I could use BCLK directly as CODEC_CLKIN. I see that if the PLL is used, the PLL_CLKOUT must be at least 80 MHz, but is it okay to use a lower CODEC_CLKIN if the PLL is not used? Also, if I set NDAC=1 and MDAC=1 and DOSR=32, I would achieve a DAC_fS of 8 kHz to equal the I2S WCLK, but is a DOSR of 32 enough for an 8 kHz sample rate?