Hello,

When TDM data is input, the device automatically selects TDM mode. Is this only the case when "SAP Control (Serial Audio-Port Control) Register (address = 0x03)" is its default setting? My customer is experiencing difficulty to reproduce TDM with SAP control configured as DSP mode.

The customer could successfully reproduce audio from I2S input, but is failing with TDM. Could you make an advice?

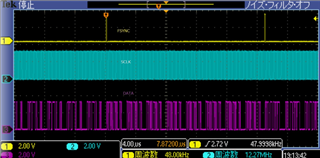

The screen shot for FSYNC, SCLK, and DATA the customer observed is shown below.

I am checking with the customer about Clock Fault.

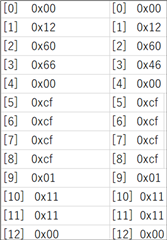

Register dump is here:

Thanks.

Regards,

Oguri (TIJ automotive FAE)