hi,

PCM4222 work in PCM mode and sclk=12.288Mhz, normal mode. sample rate is 48khz.

below is my design that produce P/N diff signal to PCM4222 analog input.

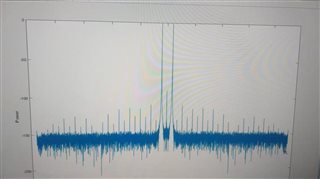

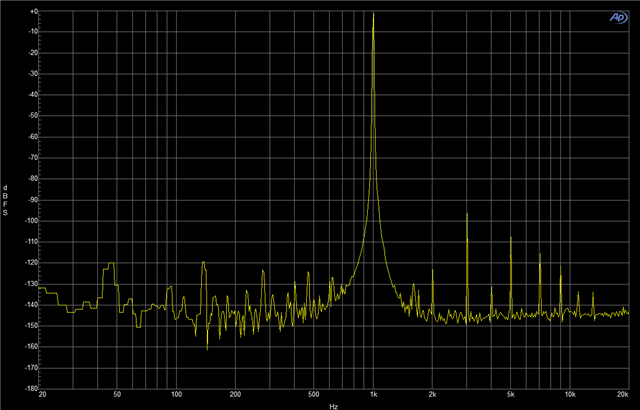

when below PCM4222_P/N port not connected to PCM4222 analog input, THD is very good about -120dbc@1khz 2.6 Vpp sin signal(measure by instrument, not through PCM4222 sample data's fft analysis).

but when PCM4222_P/N port connected to PCM4222 analog input, THD become very bad about -100dbc. and when no sclk 12.288M clock input to PIN35 master clock, THD recover to -120dbc.

i guess PCM4222 's sample hold circuit has affect amplifier's THD performance. can you help to provide some method to avoid sample hold circuit influence? thanks!

BTW, below design is not a symmetry design and maybe have some defects.