Other Parts Discussed in Thread: PCM1808

Hi team,

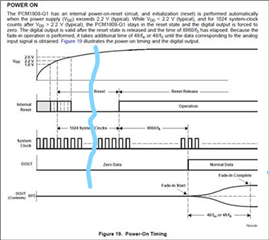

Is it OK to apply 5V to Vcc after Vdd powered up?

In my case, There is a case that Vdd applied first and then Vcc applied at the timing below in blue line.

Does the device start up correctly? Is there any concern?

regards,