Other Parts Discussed in Thread: TLV320AIC3104

HI Team

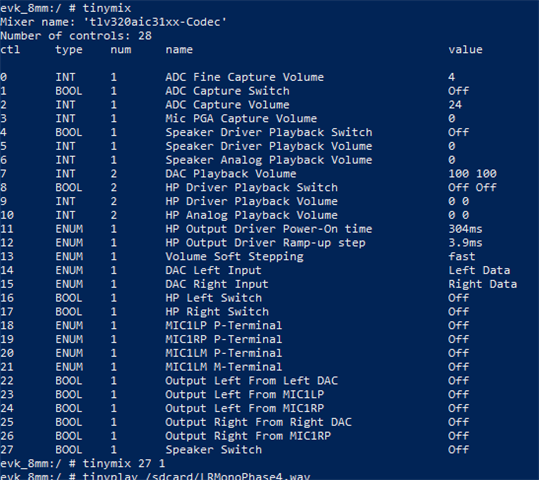

We are using tlv320aic3100 Internal codec.

facing issue related to MCLK.

Changes:

sound-tlv320aic31xx {

compatible = "simple-audio-card";

simple-audio-card,name = "tlv320aic31xx-Codec";

simple-audio-card,format = "i2s";

simple-audio-card,frame-master = <&cpudai2>;

simple-audio-card,bitclock-master = <&cpudai2>;

simple-audio-card,widgets =

"Speaker", "Speaker Jack";

simple-audio-card,routing =

"Speaker Jack", "SPK";

cpudai2: simple-audio-card,cpu {

sound-dai = <&sai1>;

};

simple-audio-card,codec {

sound-dai = <&tlv320aic31xx>;

clocks = <&clk IMX8MM_CLK_SAI1_ROOT>;

};

};

tlv320aic31xx: codec@18 {

compatible = "ti,tlv320aic3100";

reg = <0x18>;

pinctrl-0 = <&pinctrl_audio_reset_31xx>;

reset-gpios = <&gpio4 1 GPIO_ACTIVE_LOW>;

#sound-dai-cells = <0>;

ai31xx-micbias-vg = <MICBIAS_2_0V>;

HPVDD-supply = <®_3p3v>;

SPRVDD-supply = <®_3p3v>;

SPLVDD-supply = <®_3p3v>;

AVDD-supply = <®_3p3v>;

IOVDD-supply = <®_3p3v>;

DVDD-supply = <®_1p8v>;

};

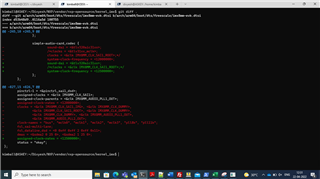

&sai1 {

pinctrl-names = "default", "dsd";

pinctrl-0 = <&pinctrl_sai1>;

pinctrl-1 = <&pinctrl_sai1_dsd>;

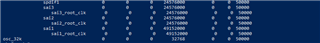

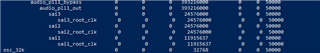

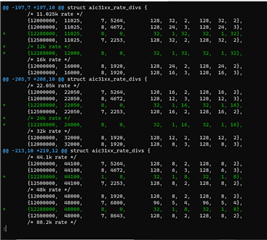

assigned-clocks = <&clk IMX8MM_CLK_SAI1>;

assigned-clock-parents = <&clk IMX8MM_AUDIO_PLL1_OUT>;

assigned-clock-rates = <12500000>;

status = "okay";

};

pinctrl_sai1: sai1grp {

fsl,pins = <

MX8MM_IOMUXC_SAI1_MCLK_SAI1_MCLK 0xd6 /*MCLK*/

MX8MM_IOMUXC_SAI1_TXFS_SAI1_TX_SYNC 0xd6 /*WCLK*/

MX8MM_IOMUXC_SAI1_TXC_SAI1_TX_BCLK 0xd6 /*BCLK*/

MX8MM_IOMUXC_SAI1_TXD0_SAI1_TX_DATA0 0xd6 /*DIN*/

MX8MM_IOMUXC_SAI1_RXD0_SAI1_RX_DATA0 0xd6 /*DOUT*/

>;

};

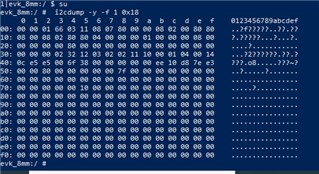

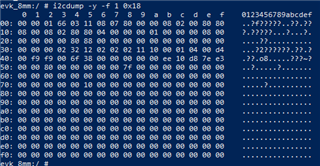

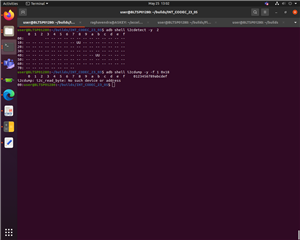

LOGS:

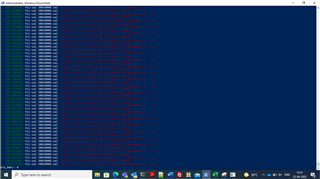

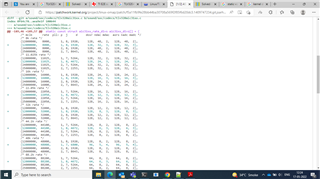

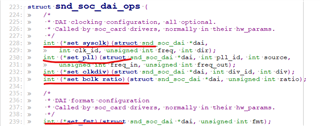

Line 406: 04-18 19:45:59.438 0 0 E tlv320aic31xx-codec 1-0018: aic31xx_set_dai_sysclk: Unsupported frequency 24576000

Line 407: 04-18 19:45:59.447 0 0 E tlv320aic31xx-codec 1-0018: ASoC: error at snd_soc_dai_set_sysclk on tlv320aic31xx-hifi: -22

Line 407: 04-18 19:45:59.447 0 0 E tlv320aic31xx-codec 1-0018: ASoC: error at snd_soc_dai_set_sysclk on tlv320aic31xx-hifi: -22

Line 408: 04-18 19:45:59.456 0 0 E tlv320aic31xx-codec 1-0018: simple-card: set_sysclk error

Line 409: 04-18 19:45:59.462 0 0 E 30010000.sai-tlv320aic31xx-hifi: ASoC: error at snd_soc_link_init on 30010000.sai-tlv320aic31xx-hifi: -22

Line 409: 04-18 19:45:59.462 0 0 E 30010000.sai-tlv320aic31xx-hifi: ASoC: error at snd_soc_link_init on 30010000.sai-tlv320aic31xx-hifi: -22

Line 410: 04-18 19:45:59.473 0 0 W asoc-simple-card: probe of sound-tlv320aic31xx failed with error -22

Thanks

Divyesh.