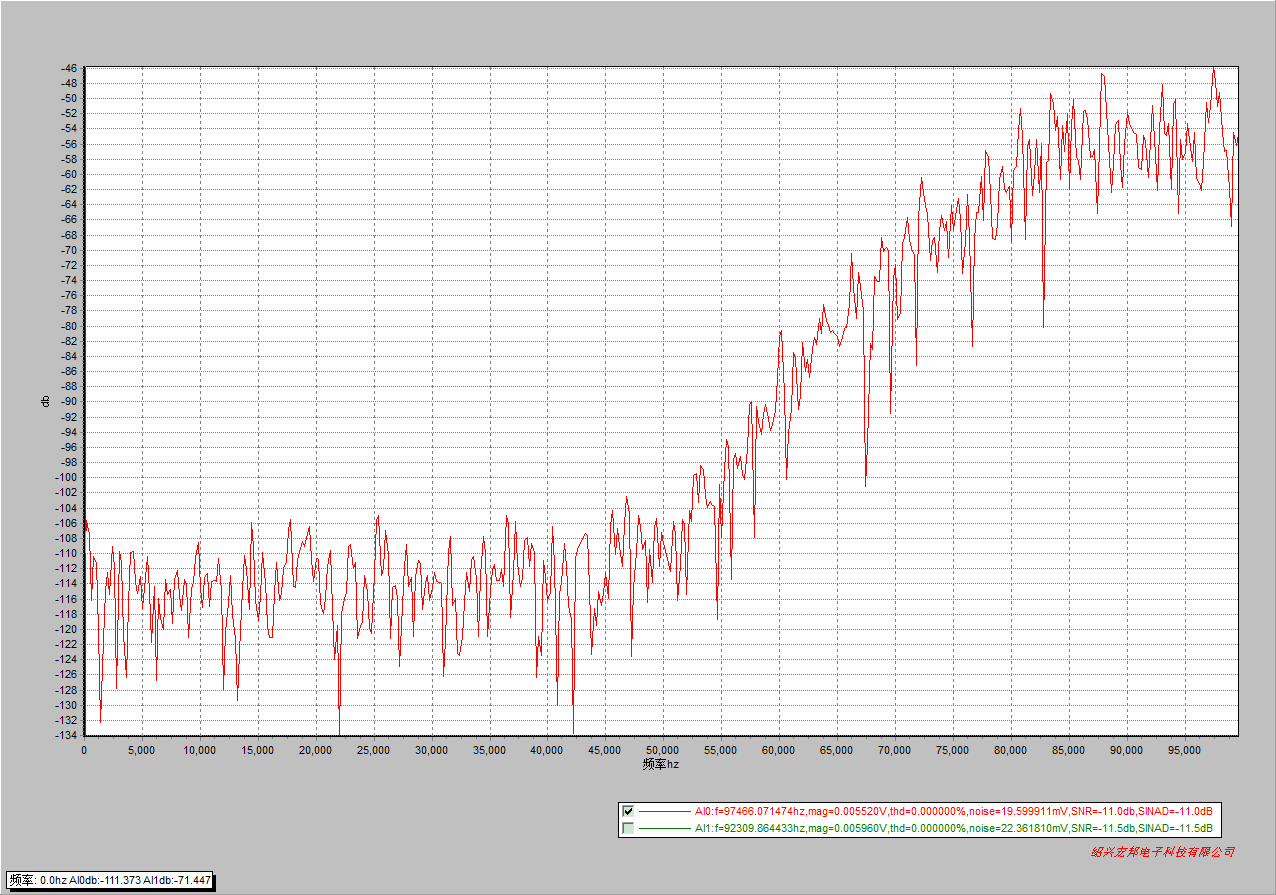

PCM4202 works in the PCM Slave Mode Operation or PCM master Mode Operation. I found that quad Rate Mode (LRCK=200KHz,SCKI= 128FS,BCK= 64FS) had high noise, while other modes had low noise.Figure 1 shows the corresponding FFT diagram.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.