Hello,

We are attempting to use the PCM1864 in our amplifier, however we are getting a lot of white noise and distortion coming out on the speakers when we are either providing an audio signal or nothing, and we have narrowed it down to being a problem with the ADCs.

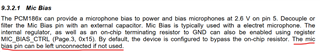

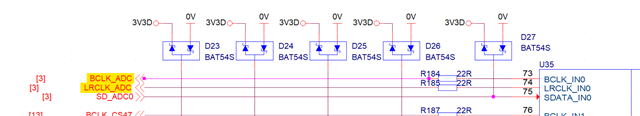

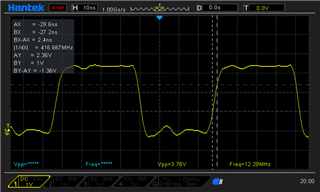

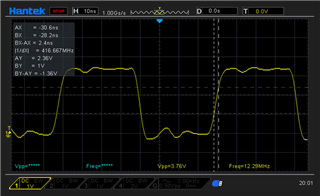

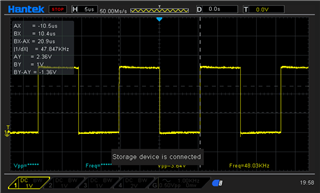

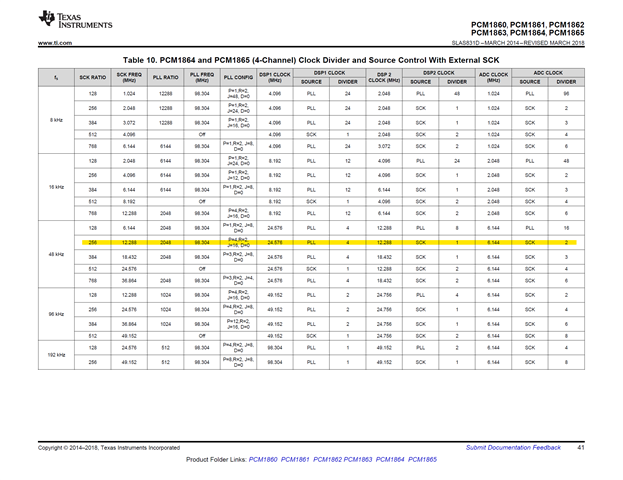

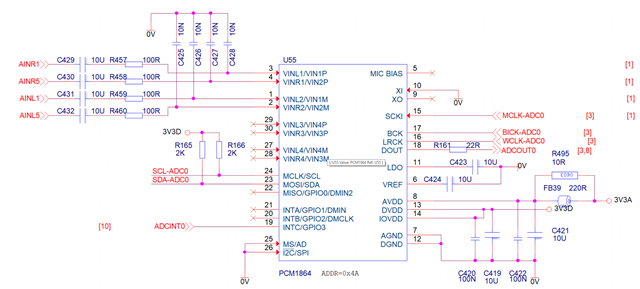

There are 4 PCM1864s, each handling 2 pairs of stereo inputs, they are all in slave mode with the clocks (SCK, BCK and LRCK) being provided by a DSP, an ADAU1467 from Analog Devices, and the DSP is connected to a 12.288MHz crystal. We communicate to the ADCs by I2C and use that to configure the setup of the ADCs. As for the configuration of the ADCs, as mentioned before they are in slave mode and we configure the clocks to follow row 12 of table 10 on page 41 from the datasheet, see the highlighted below:

We also configure the mapping of the inputs to match our hardware setup, the Serial Audio Interface Format to be TDM, 4 channel TDM transmission data and the TDM offset to 1 BCK (same as I2S), all other register configurations are left as their default.

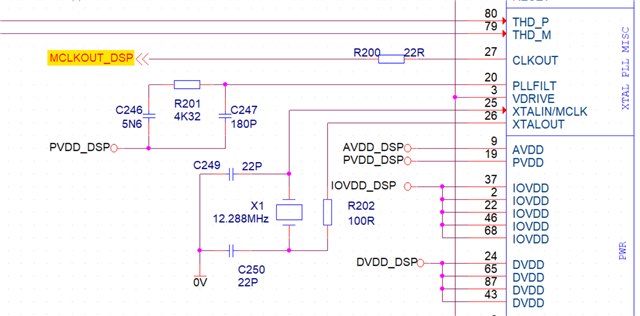

We have tested the system beyond the ADCs by having the DSP generate a test chime and there is no noise or distortion on the chime, so we know that the issue is to do with the ADCs, either how we are configuring the registers or with the hardware design. Our design for the inputs to the ADCs is similar to what is shown in your datasheet, only a slightly variation in resistor and capacitor values, however we have tried changing those values to match the datasheet, but that didn't have any effect on the audio quality, so we don't think the problem is with the inputs to the ADCs. Here is a picture of our schematic for one of the ADCs:

We would appreciate any help or pointers to get us to a solution for this problem.

Thank you