Hi Experts,

Our customer have a concern as shown below:

"I'm developping a multichannel amp for beamforming puposes for a german pro audio equiper.

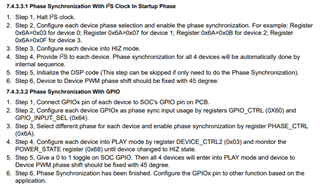

I want to pwm phase sync 4 TAS5825m with GPIO pin 0 as trigger. I already worked with the phase sync with I2S clocks stop and restart as trigger. See the corresponding e2e thread: https://e2e.ti.com/support/audio-group/audio/f/audio-forum/906307/tas5825m-multi-device-pwm-phase-sync

My setup: Housekeeping process flow, with OTFB and hybrid modulation enabled; amps in hiZ. I write the exported c header sequence to the amps and configure the phase sync afterwards.

The amps enter the phase sync mode as expected. They go to HiZ mode and when I trigger the GPIO the amps go to play mode. I configured different phases for every amp.

The problem: all 4 amps have Phase setting 0, although their registers are configured correctly. I checked that by reading back the reg values.

I already checked if the phase sync doesn't work, but if I comment out my sync sequence the amps have a random phase.

See important parts of my code below (example for one amp; all amps are initialised in a loop):

//Definitions -------------------------------------------------- #define GPIO_CTRL_REG 0x60 //all gpio pins are inputs by default, datasheet p. 67 #define GPIO2_INPUT (0 << 2) #define GPIO2_OUTPUT (1 << 2) #define GPIO1_INPUT (0 << 1) #define GPIO1_OUTPUT (1 << 1) #define GPIO0_INPUT (0 << 0) #define GPIO0_OUTPUT (1 << 0) #define GPIO0_SEL_REG 0x61 #define GPIO1_SEL_REG 0x62 #define GPIO2_SEL_REG 0x63 #define GPIO_WARNZ (0b1000) #define GPIO_FAULTZ (0b1011) #define GPIO_INPUT_SEL_REG 0x64 #define GPIO0_PHASE_SYNC 0b10000 #define GPIO0_MUTEZ 1 //----------------------------------- #define POWER_STATE_REG 0x68 //datasheet p. 73 #define POWER_STATE_DEEPSL 0 #define POWER_STATE_SLEEP 1 #define POWER_STATE_HIZ 2 #define POWER_STATE_PLAY 3 //----------------------------------- #define PHASE_CTRL_REG 0x6a //Device to device phase sync reg //sync trigger set to gpio, sync enabled, datasheet p. 74 #define PHASE0 0b0001 #define PHASE45 0b0101 #define PHASE90 0b1001 #define PHASE135 0b1101 //--------------------------------------------------------------------------- //Init sequence ------------------------------------------------------------- const uint8_t Amp_pwm_phases[4] = {PHASE0, PHASE45, PHASE90, PHASE135}; //set PDN pin high, enable amps PDN_Set(); Delay_ms(5); //send basic reg config from PPC3 software //config: Housekeeping process flow, hybrid modulation, HiZ mode, unmuted tas5825_send_reg_config(x, registers, sizeof(registers)/sizeof(registers[0])); uint8_t data[2]; //switch to page 0 and book 0 tas5825_change_page(amp_index, 0); tas5825_change_book(amp_index, 0); //Configure GPIOx pin direction data[0] = GPIO_CTRL_REG; data[1] = (GPIO0_INPUT | GPIO1_OUTPUT | GPIO2_OUTPUT); I2C2_Write(Amp_addresses[amp_index], data, 2); //Configure GPIO0 to phase sync data[0] = GPIO_INPUT_SEL_REG; data[1] = GPIO0_PHASE_SYNC; I2C2_Write(Amp_addresses[amp_index], data, 2); //Select different phase and enable phase synchronization data[0] = PHASE_CTRL_REG; data[1] = Amp_pwm_phases[amp_index % 4]; I2C2_Write(Amp_addresses[amp_index], data, 2); //Set device to play mode tas5825_set_device_state(amp_index, STATE_PLAY, DSP_UNMUTE, DSP_NORMAL_OP); //Monitor POWER_STATE register until device changed to HIZ state uint8_t device_state = 0; do { if (amp_index < 4) I2C2_Read(Amp_addresses[amp_index], POWER_STATE_REG, &device_state, 1); else I2C3_Read(Amp_addresses[amp_index], POWER_STATE_REG, &device_state, 1); } while(device_state != POWER_STATE_HIZ); Delay_ms(20); //set gpio pin high, amps will enter play mode GPIO0_Set();

Are there any special points that are not mentioned in the sequence described in the datasheet? I also tried it with BD modulation, but it is the exact same issue."

I hope you can help us.

Best regards,

Gerald