Other Parts Discussed in Thread: TLV320ADC3120

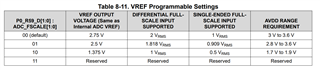

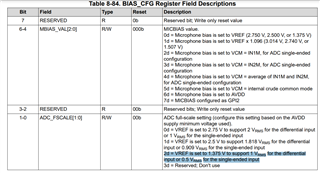

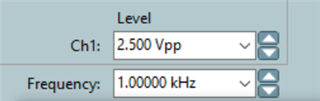

TLV320ADC3120 power supply 1.8V, set to single-ended input mode, 10 kΩ input impedance, HPF setting 0.00025fs, input 2.5v peak-to-peak, 1.25v bias sine wave signal,

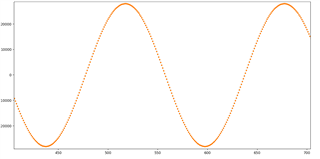

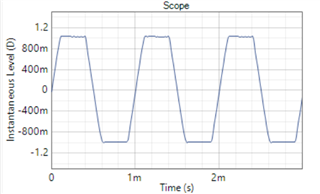

The ADC can normally sample the sine wave without distortion, which is inconsistent with the 0.5v RMS input range described in the manual under the 1.8V power supply. The following are the time domain and spectrograms during the test.