- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi TI Team,

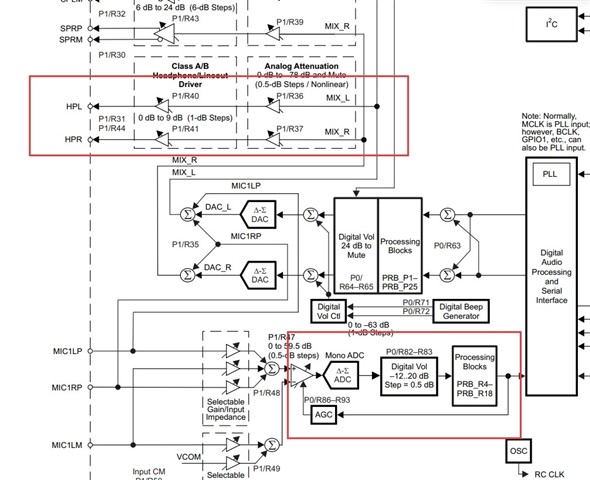

At present, we can use TLV320AIC3110 chip to independently switch on the recording module (ADC), loop out module (HPL & HPR),

However, when loopout and recording are enabled at the same time, that is, when the functions of the two modules marked in the figure are enabled, loopout function will produce recording effect

Impact, recording files have relatively large noise.

Attached "TLV320AIC3110 Recording Noise problem.docx" is debugging related data, as well as recording files in two cases.

Please help to deal with this problem.

Click here to play this audio clipClick here to play this audio clipTLV320AIC3110 Recording noise problem.docx

Hi Ken,

It sounds like the output from the HPL/HPR pins is being recorded by the MIC input pins. Make sure that your mic is sufficiently far away from your speakers to prevent audio coupling.

What does test_err and test_ok mean on your audio files?

Thank you,

Jeff McPherson

Hi Jeff,

Thank you for your reply,

I do not think the output from the HPL/HPR pins is being recorded by the MIC input pins, even if I unplug the loop speaker, as long as I turn on the 'HP Right Switch' or 'HP Left Switch' with amixer, it will have a large noise on the ADC recording.

The audio files of test_ok and test_err are both recording files. the following shows the different:

the test_ok corresponds to when HPL&HPR is turned off, only the ADC recording function is enabled, in this case, the register val is:

page0:

No size specified (using byte-data access)

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 00 00 01 56 03 11 08 00 00 00 00 08 02 00 80 80 ..?V???....??.??

10: 08 00 08 02 80 80 04 00 00 00 01 00 00 00 08 00 ?.?????...?...?.

20: 00 00 00 00 00 00 00 0a 00 00 00 00 00 00 00 00 .......?........

30: 00 00 00 02 32 12 03 02 02 11 10 00 01 08 00 14 ...?2??????.??.?

40: 0c 00 00 00 6f 38 00 00 00 00 00 ee 10 d8 7e e3 ?...o8.....???~?

50: 00 00 00 00 00 00 00 00 7f 00 00 00 00 00 00 00 ........?.......

60: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

c0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

page1:

No size specified (using byte-data access)

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 01 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ?...............

10: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 16 ...............?

20: 06 3e 00 32 00 00 7f 7f 06 06 00 00 20 86 02 80 ?>.2..????.. ???

30: a0 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ?...............

40: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

50: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

60: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

c0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

and the test_err corresponds to when HPL&HPR and ADC is turned on at same time, in this case, the register val is:

page0:

No size specified (using byte-data access)

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 00 00 01 56 03 91 08 00 00 00 00 88 82 00 80 80 ..?V???....??.??

10: 08 00 88 82 80 80 04 00 00 00 01 00 00 00 88 00 ?.?????...?...?.

20: 00 00 00 00 00 22 00 00 00 00 00 00 00 00 00 00 ....."..........

30: 00 00 00 02 32 12 03 02 02 11 10 00 01 08 00 14 ...?2??????.??.?

40: 0c 00 00 00 6f 38 00 00 00 00 00 ee 10 d8 7e e3 ?...o8.....???~?

50: 00 00 00 00 00 00 00 00 7f 00 00 00 00 00 00 00 ........?.......

60: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

c0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

page1:

No size specified (using byte-data access)

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 01 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ?...............

10: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 d6 ...............?

20: 06 3e 00 32 80 80 7f 7f 07 07 00 00 20 86 02 80 ?>.2??????.. ???

30: a0 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ?...............

40: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

50: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

60: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

c0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

Hi Paul,

Thank you for the clarification. Can you also share the schematic and layout of your system?

Thank you,

Jeff McPherson

Hi Jeff,

You can see the schematic of the codec section in file of "tlv320aic3110layout.pdf".tlv320aic3110layout.pdf

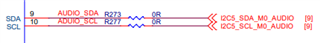

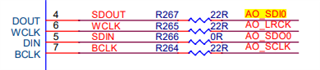

The codec is attached to our main SOC via i2c5.

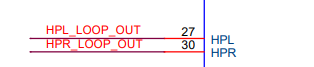

In addition, after audio capture with the MIC pin(MICLP&MICRP), one way of MIC data through HPR & HPL loop-out playback,

and the other way through the ADC recording and then into our main chip with i2s

Thank you

Hello Paul,

I will continue to help on this issue. Based on the register configuration there is nothing that indicates an issue with your settings. If possible, can you share PCB layout files? With the layout files we can see if there is an issue with any noise coupling onto the traces.

If you do not want to share the files on the forum, we can share them over email.

Best,

Andrew

Hi Paul,

I can reach out to you. Is the email you used for your myTI Account a good email to reach out at?

-Andrew

Hello Paul,

Sorry for the delay and thank you for sharing the board files over email. The layout looks good and there doesn’t seem to be any issues here. I took a look at the register ouputs again and noticed that from the test_ok register dump that the PLL and clock dividers are powered down and for test_err these are powered up. It also looks like that even when the ADC is powered on you have selected max attenuation on the channel. So that even if there was signal coming form the ADC it would be almost negligible. To me this suggest the following:

Best,

Andrew