Hello,

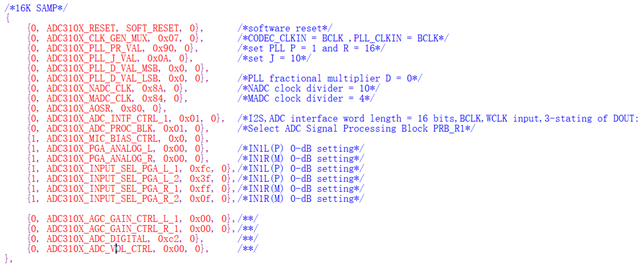

Our customer used TLV320ADC3101-Q1 for his application, sampling rate is 32Kbps, Generating Master Clock from BCLK,

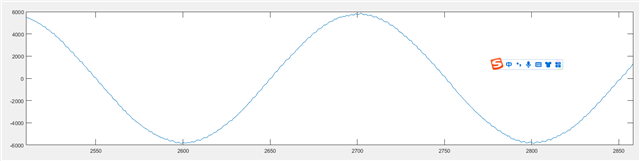

The captured data of ADC output which drew with MATLAB is not smooth as this:

Best regards

kailyn

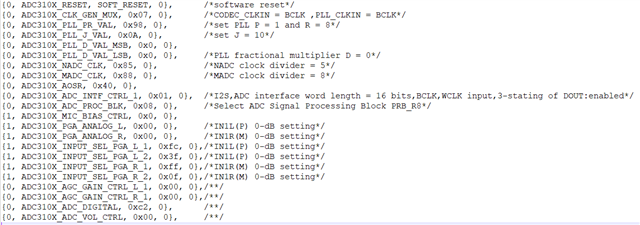

But if configured 16Kbps sampling rate, the captured curve is smooth.