Hi, Support Team

We saw the Application Report:SBAA415 Multiple PCm6xx0 Devices With Shared TDM and I2C Bus

we have 2 question as below

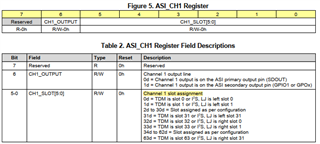

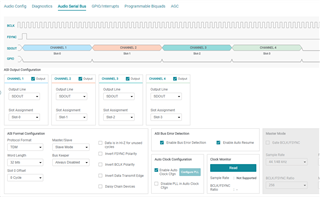

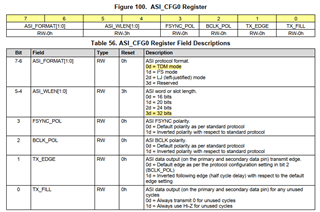

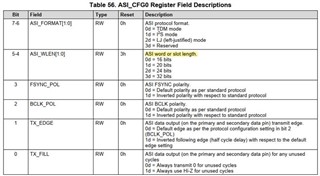

Q1: Setting ADC of Word(Slot) Length, the ADC can read TDM slot?

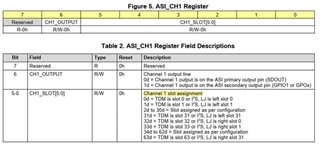

Q2: about setting ADC of Channel Slot Assignment ,so the ADC can appoint each one analog channel data to TDM slot?

if any suggestion, Please advise me.

Thanks,

Best regards,

Lawrence