Other Parts Discussed in Thread: TAS5827, TAS5805MEVM

Dear Sirs and Madams,

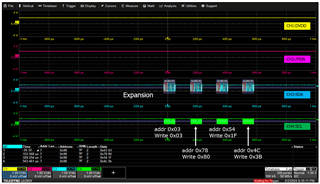

We are verifying the I2C communication of TAS5825.

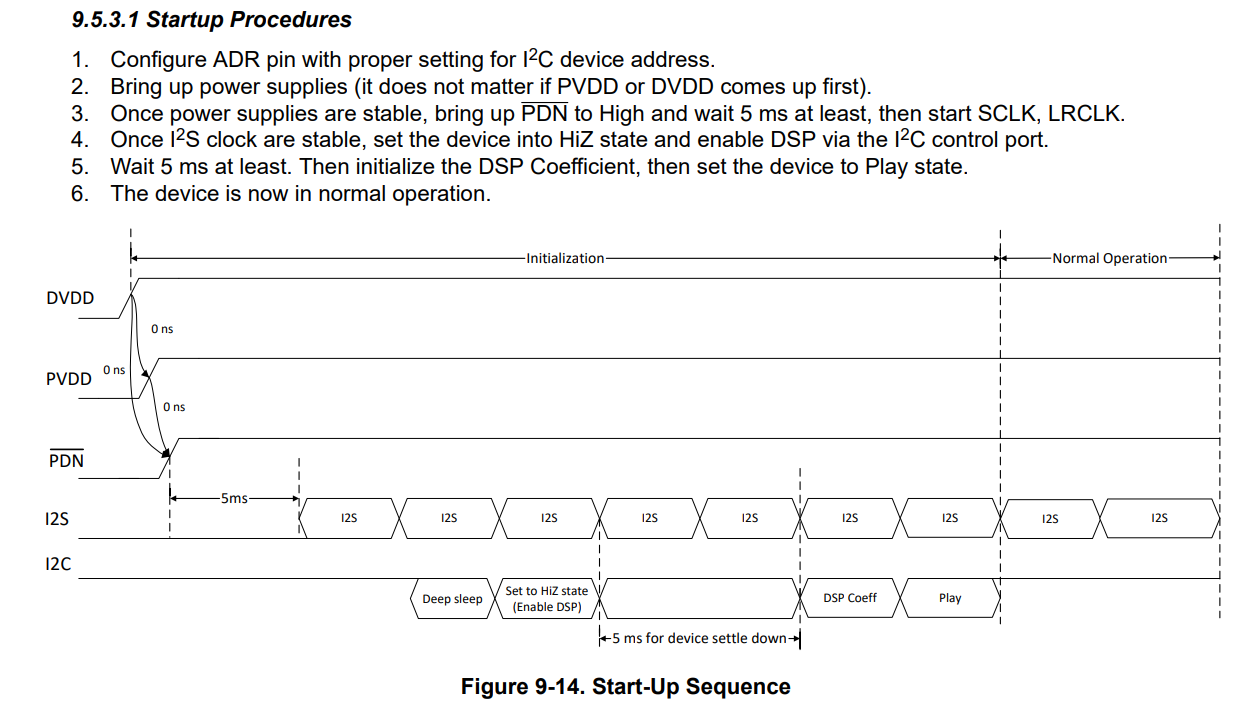

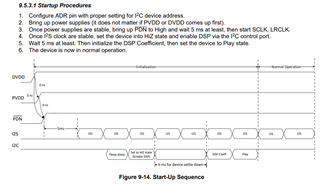

Page 42 of the datasheet describes "9.5.3.1 Startup Procedures", but I would like to confirm two points.

1. Is it correct that I2C communication becomes valid 5ms after *PDN is asserted to High?

2. Is it correct to think that I2C and I2S are independent?

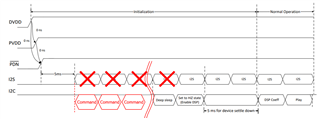

I understand that "9.5.3.1 Startup Procedures" is just the I2S operation start sequence, and that I2C commands can communicate 5ms after *PDN goes High, as shown in red in the figure below. Is this recognition correct?

/* TAS5825M datasheet URL */

Regards,

MM