Other Parts Discussed in Thread: PCM3168

Hi,

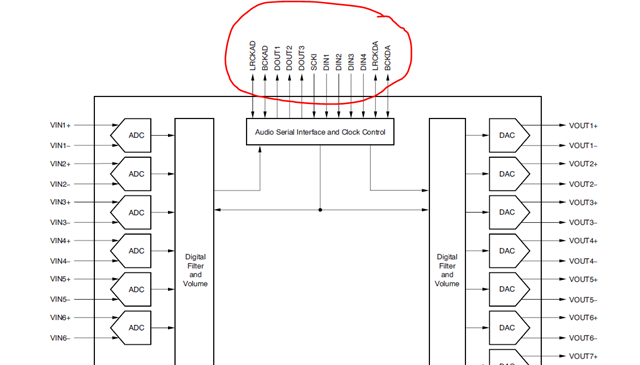

We are replacing CS42436 with PCM3168A

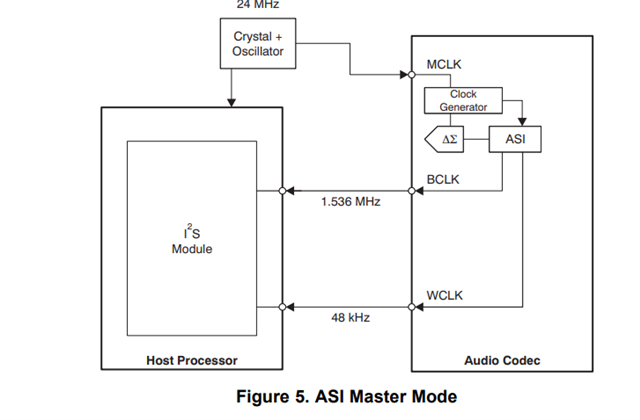

We are using ADSP BF527 SPORT for TDM data.

Codec is in slave Mode and operating in single speed mode (SSM)

please can you help on physical interface between PCM3168A and ADSP BF527

Thanks & Regards,

Arvind Khalate