Hi team,

Here's an issue may need your help:

We encountered an issue when using the TLV320AIC3204 DAC chip. Whether playing audio through HPL/R or LOL/R, there will be noise. Specifically manifested as:

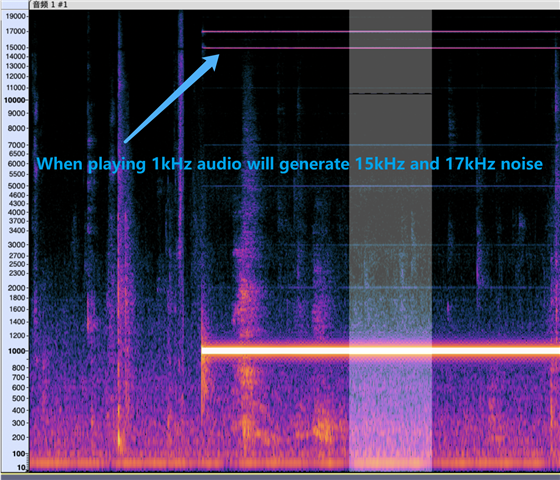

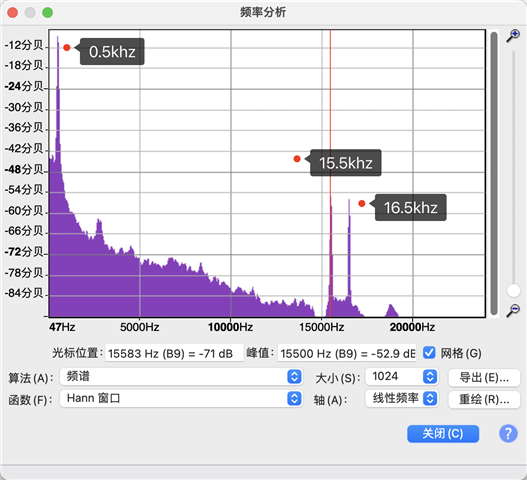

1. Playing 0.5kHz audio will generate 15.5kHz and 16.5kHz noise. (see attached spectrogram)

2. Playing 1kHz audio will generate 15kHz and 17kHz noise.

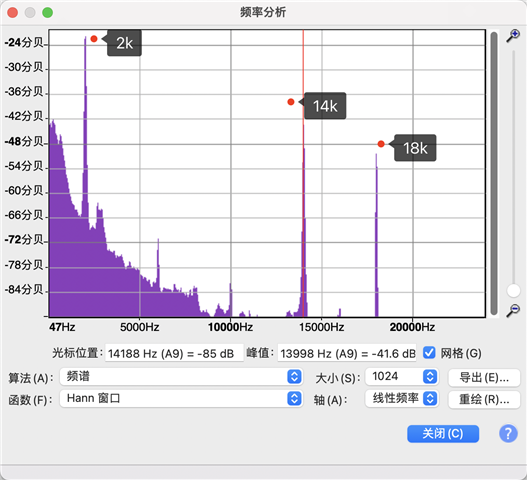

3. Playing 2kHz audio will generate 14kHz and 18kHz noise.

This IC is how we use it:

Send a 0.5kHz/1kHz/2kHz sine signal with a sampling rate of 16KHz and a 16bit depth to a MCU via USB audio interface,

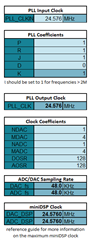

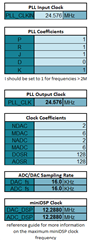

After converting the sound into 32 bit depth, the MCU sends it to the DAC via i2s. The MCLK is 24.576 mhz, the LRCLK is 16 kHz, and the BCLK is 1.024 mhz

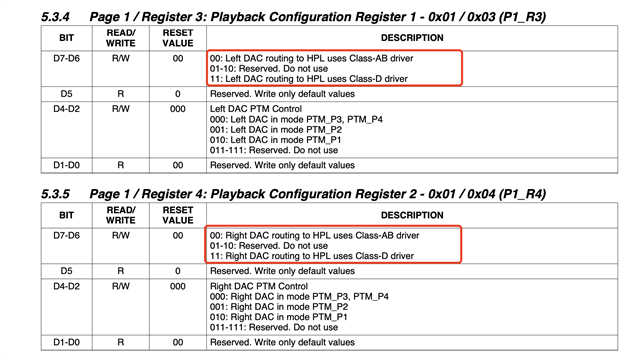

The dac configuration is as follows:

Best Regards,

Linus