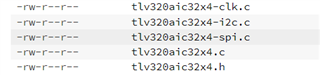

Other Parts Discussed in Thread: TLV320AIC3254

Hi Teams,

We use TI TLV320AIC3254-Q1 on the Qualcomm SA525M platform

Driver seems to have brought up

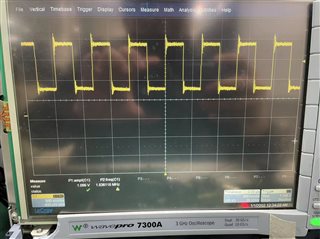

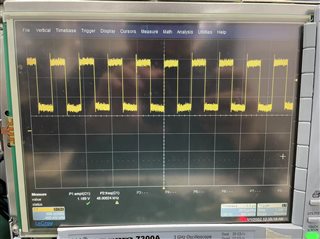

Using TERTIARY MI2S

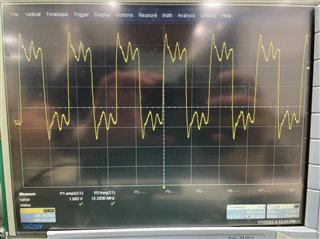

But when playing the sound, a log like this will appear

Please help us for this log check, Thank you so much.

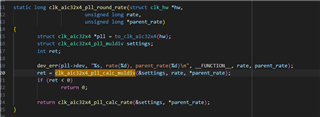

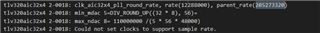

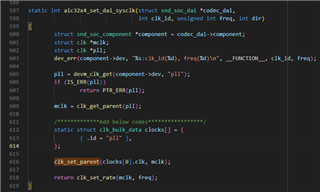

[ 480.977973][ T1486] aic3x_hw_params(): unable to setup PLL

[ 480.984100][ T1486] tlv320aic3x 2-0018: ASoC: error at snd_soc_dai_hw_params on tlv320aic3x-hifi: -22

[ 480.994214][ T1486] MI2S-LPAIF-RX-TERTIARY: ASoC: soc_pcm_hw_params() failed (-22)